# THE DESIGN OF A MULTIPROCESSOR DEVELOPMENT SYSTEM

# Thomas Lee Anderson

© Massachusetts Institute of Technology

September 1, 1982

This research was supported by the Advanced Research Projects Agency of the Department fo Defense and was monitored by the Office of Naval Research under contract number N00014-75-C-0661.

Massachusetts Institute of Technology Laboratory for Computer Science

Cambridge

Massachuetts 02139

# The Design of a Multiprocessor Development System

by

#### Thomas Lee Anderson

Submitted to the Department of Electrical Engineering and Computer Science on September 1, 1982 in partial fulfillment of the requirements for the Degree of Master of Science in Electrical Engineering and Computer Science

#### **Abstract**

A multiprocessor development system has been designed and a prototype system is being constructed. The system, known as Concert, is intended to support multiprocessor research efforts at M.I.T. The motivation for Concert and the project history are summarized briefly. Some intended applications are also identified.

The system incorporates the RingBus architecture, a novel scheme for interconnecting processors and memory in a tightly-coupled multiprocessor system. The architecture is described both in its general form and in the particular implementation used in the system. The results of some analysis and synthesis of the architecture are summarized.

The design of the Concert multiprocessor development system is described, with particular emphasis on the tradeoffs considered in the design process. The design of two particular hardware modules is discussed in considerable detail. Finally, some suggestions are offered for future use of the system and further investigation into the RingBus architecture.

Name and Title of Thesis Supervisor:

Robert H. Halstead, Jr., Assistant Professor of Computer Science and Engineering

Key Words and Phrases:

multiprocessor systems, segmented computer buses, parallel processing, computer architecture

# **Acknowledgements**

There are numerous people whose assistance on the Concert project was instrumental in the completion of this thesis. The project leaders, Richard Zippel and Robert Halstead, provided constant guidance throughout all phases of the project. The software members of the team — Dave Alpern and John Morrison — have contributed in numerous ways to the project. Tom Sterling, who intends to use the system for his own thesis work, assisted with suggestions on several aspects of the hardware design, particularly hardware monitoring. His interest as a potential user has helped to insure that we stayed on the track of making the system a useful tool for the M.I.T. computing community.

The Real Time Systems Group, under the leadership of Steve Ward, has provided both a special place to work and a great deal of assistance. The hardware expertise of numerous members of the group has undoubtedly helped me to avert some major problems. The group also provided the computing facilities and text processing capabilities to produce this thesis. The support of Michael Dertouzos, Director of the Laboratory for Computer Science, has also been crucial. Without his assistance in obtaining funds for both students and hardware, it would have been impossible to construct a prototype system.

My officemate Jim Troisi deserves thanks for his assistance in spicing up my arbiter simulator and for his interest in the project and willingness to hear my complaints and problems. Finally, I owe a special debt to my thesis advisor, Bert Halstead. Bert's RingBus Architecture provided the basis for most of the interesting aspects of the system design, and his suggestions on the design itself were frequent and helpful. It is largely because of his encouragement and drive that I was able to complete this thesis.

# TABLE OF CONTENTS

| 1: Introduction                                                             |   | , , <b>7.</b> |

|-----------------------------------------------------------------------------|---|---------------|

| 2: Background on the Concert Project 2.1: Multiprocessor Research at M.I.T. |   | 9.<br>9.      |

| 2.2: Project History                                                        |   | 11.           |

| 2.3: Suggested Applications                                                 |   | 12.           |

| 2.4: Design Goals                                                           |   | 14.           |

| 3: The RingBus Architecture                                                 |   | 16.           |

| 3.1: Dimensions of Multiprocessing                                          |   | 16.           |

| 3.2: The General RingBus Architecture                                       |   | 20.           |

| 3.3: Analysis of the RingBus Architecture                                   |   | 22.           |

| 3.3.1: Major Implementation Options                                         |   | 23.           |

| 3.3.2: Requesting and Granting                                              |   | 24.           |

| 3.3.3: The Role of the Arbiter                                              |   | 27.           |

| 3.3.4: Arbiter Priority Schemes                                             |   | 30.           |

| 3.3.5: Arbitration Algorithms                                               |   | 35.           |

| 3.4: Simulation of the RingBus Architecture                                 |   | 43.           |

| 4: The Concert System Architecture                                          |   | 49.           |

| 4.1: The Concert RingBus Implementation                                     |   | 49.           |

| 4.1.1: The Node                                                             |   | 50.           |

| 4.1.2: The Slice                                                            |   | <b>52</b> .   |

| 4.1.3: The Ring                                                             |   | 55.           |

| 4.1.4: Multi-Ring Systems                                                   |   | 56.           |

| 4.2: Concert Terminology                                                    |   | 56.           |

| 4.3: The Concert Address Space                                              |   | 58.           |

| 4.4: Definition of the RingBus                                              |   | 63.           |

| 5: The Design of the RingBus Interface Board                                | • | 68.           |

| 5.1: Global Registers                                                       |   | 68.           |

| 5.1.1: The Slice Reset Register                                             |   | 69.           |

| 5.1.2: The Node Interrupt Registers                                         |   | 70.           |

| 5.1.3: The Slice Protection Register                                        |   | 71.           |

| 5.1.4: Support for Hardware Monitoring                                      |   | <b>72</b> .   |

| 5.1.5: Global Register Addresses                                            |   | 76.           |

| 5.2: Access Control                                                         |   | 77.           |

| 5.2.1: Basic Requirements                                                   |   | 78.           |

| 5.2.2: Access Path Options                                                  |   | 79.           |

| 5.2.3: The Arbiter Interface                                                |   | 85.           |

| 5.3: Access Support                                                         |   | 86.           |

| 5.3.1: Bus Interfaces                                                       |   | 87.           |

| 5.3.2: Support for Atomic Operations                                        |   | 89.           |

| 5.3.3: Abort Operations on the RingBus                                      |   | 90.           |

Contents

# The Design of a Multiprocessor Development System

| 5.4: Multibus Arbitration            | 91.  |

|--------------------------------------|------|

| 6: The Design of the RingBus Arbiter | 93.  |

| 6.1: Overview of the Arbiter         | 93.  |

| 6.2: Examining the Requests          | 96.  |

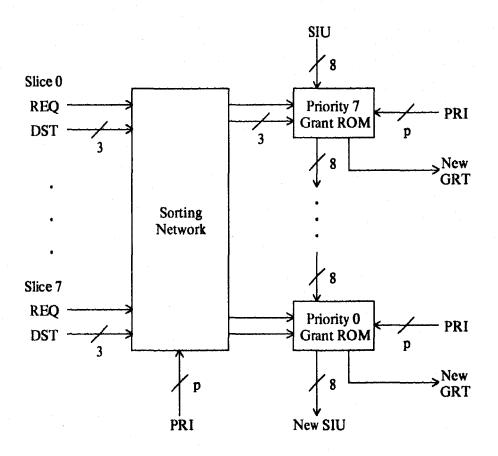

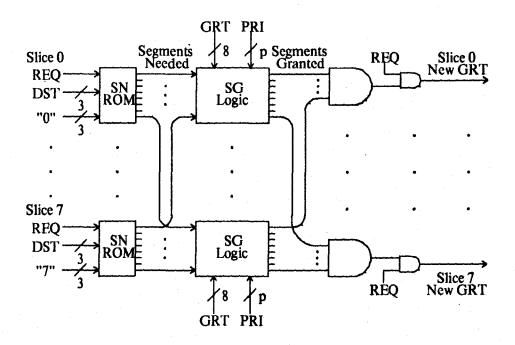

| 6.3: Granting the Requests           | 99.  |

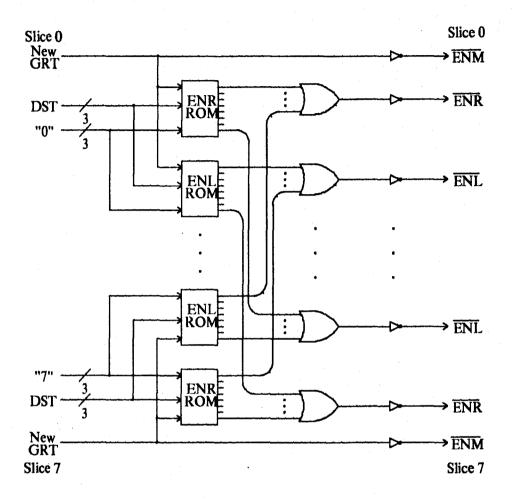

| 6.4: Generating the Enable Signals   | 106. |

| 6.5: The Final Design                | 107. |

| 6.5.1: The Arbitration Scheme        | 107. |

| 6.5.2: Flexibility                   | 112. |

| 6.5.3: Practical Issues              | 113. |

| 7: Conclusions                       | 116. |

| 7.1: Summary                         | 116. |

| 7.2: Suggestions for Future Research | 117. |

| Bibliography                         | 119. |

|                                      |      |

6. Contents

**Chapter 1: Introduction**

Several months ago, a research group was formed under the auspices of the Real

Time Systems Group in the Laboratory for Computer Science at M.I.T. to develop a

multiprocessor development system. The system, now known as "Concert," is intended

as a tool to allow researchers at M.I.T. to experiment with multiprocessing ideas and

concepts on a working multiprocessor system. A prototype version of this system has

been designed and is now under construction.

This thesis documents the hardware design of the prototype system. It starts by

providing background on the project and the motivation for Concert in Chapter 2.

There has been considerable interest within the M.I.T. computing community in the use

of the system for a variety of applications. Chapter 2 briefly discusses many of these

applications, some of which will be undertaken within the next few months.

The design of the Concert multiprocessor development system is outlined from two

angles. First, Chapter 3 describes the RingBus architecture, a scheme for intercon-

necting processors and global memory in a tightly-coupled multiprocessor system.

Some effort was spent in analyzing and simulating this architecture, and the results of

this work are summarized.

The remainder of the thesis describes the system that is being constructed. The

system is interesting both in its own right — as a multiprocessing research vehicle for

the M.I.T. computing community - and as the first hardware implementation of the

RingBus architecture. Chapter 4 describes the implementation at the block-diagram

Chapter 1: Introduction

7.

level and identifies the major components of the design effort.

The thesis project primarily involved the design of two hardware modules, and these are discussed in considerable detail in Chapters 5 and 6. Particular attention is paid to the tradeoffs considered in the design process and the reasons particular implementation decisions were made. The thesis is intended to document the system as it currently exists, but also to be an interesting case study in hardware design.

Finally, Chapter 7 concludes the thesis by evaluating the current state of the Concert project and the future usefulness of the system. Some suggestions are offered for future applications work on the multiprocessor development system as well as for more investigation into the RingBus architecture.

# Chapter 2: Background on the Concert Project

This chapter describes the effort to build a multiprocessor development system at M.I.T. After establishing the research framework for the use of such a system, it gives a brief history of the project and lists some potential applications which guided the system specification.

### 2.1: Multiprocessor Research at M.I.T.

It is a truism of computer science that single processors are reaching the limits of their performance. Such fundamental physical constants as the speed of light place hard limits on the speed which a single computer can ever attain, and industry is fast approaching these limits on several fronts. Given this, a considerable portion of current research in computer science and engineering is devoted to the design and analysis of multiprocessor systems. There are several foci for this research, including multiprocessor programming models, distributed processing, and multiprocessor architectures.

Like many other research institutions, M.I.T. is actively engaged in a wide range of multiprocessing research. Several groups are studying architectures for multiprocessor systems; others are working on the software aspects of multiprocessing, including operating systems, parallel algorithms and fault-tolerance. Many more people are doing research not in multiprocessing *per se*, but rather in applications which are particularly

well-suited for implementation in a multiprocessing environment.

At the present time, most research of this nature is carried out by software simulation. The task of simulating parallel execution of multiple processors is not difficult in theory, except for a few thorny timing and synchronization issues. The problem is that software simulation is a painfully slow method for testing parallel programs. Even on fairly fast machines, the time necessary for simulation of realistic programs is tremendous.

The reason for this is simple. If a single processor computer is used to simulate a multiprocessor of many nodes, the simulator must sequentially execute tasks intended to be performed in parallel. The problem is compounded if the computer must be time-shared with other users, as is generally the case at M.I.T. However, if a working multiprocessor is available to these researchers, at least some of the parallelism in the application programs can be exploited in hardware rather than merely simulated. The multiprocessor development system was conceived to satisfy exactly this need.

The goal of the project has been to provide researchers with a readily-available multiprocessor system on which to work. The system will be particularly useful for groups who want to investigate the use of multiprocessors, but don't wish to spend a large amount of time on the construction of a system. For people investigating parallel algorithms or distributed software, the system will provide an actual multiprocessor on which to try out their ideas.

Concert also has some potential uses for research groups interested in multiprocessor architectures. They can use software to simulate their architecture or processor interconnection strategy while still exploiting the inherent parallelism of the multiprocessor. The system can effectively serve as a stepping stone for those groups who are interested in ultimately building their own hardware.

The motivation for the project is the dream of an easily-configured off-the-shelf multiprocessor system available to the M.I.T. computing community. The ultimate scenario is fairly simple. A standard processing node will be designed which can be connected with other nodes of like kind in an arbitrarily large multiprocessor system. A large supply of these nodes will be available from the supply room, already built, tested, and ready to be plugged together. Although the final design of the system will be reached by compromise among interested parties, it will have enough features to make it useful for a large number of engineers and computer scientists at M.I.T.

This brief description captures the essence of a multiprocessor development system — availability and ease of use. The intent is that people engaged in research involving multiprocessors will not have to spend time building and debugging their own systems. They can just grab fifty or a hundred processing nodes, connect them together in a configuration suitable for their particular needs, and begin playing. This need not be the ultimate system for them, but rather a "quick and dirty" way to check out theories, run benchmarks and experiment in general.

### 2.2: Project History

Discussion on the construction of a multiprocessor development system began in mid-1981 in the Real Time Systems Group. Rich Zippel organized a group to investigate the project, and by the end of the year the specification of the system was well under way. The term "multiprocessor development system" was coined as an analog

to so-called microprocessor development systems. After several earlier choices the name "Concert" was selected. It is intended to invoke an image of multiple processors performing independent tasks, but with all tasks aimed at solving a common problem.

The original proposal called for a network of independent processing nodes interconnected by dedicated serial lines. Two major problems with this approach — limited

interprocessor communication speed and difficulty in down-line loading code — led to

the choice of a shared-memory system instead. The first such system proposed was

based on a hierarchical bus structure. The amount of hardware necessary to support

this scheme was excessive, and the concern was voiced that bus contention would

severely limit performance.

The crucial juncture in the project occurred early in 1982, when Bert Halstead suggested a circular segmented bus as the top-level interconnection scheme for the system. His approach was dubbed "the RingBus architecture," and has been incorporated into the Concert prototype. The next chapter describes the architecture in detail, but it is worth noting here that its attractiveness lies in its ability to support simultaneous accesses to global memory.

# 2.3: Suggested Applications

From its inception, Concert was intended to be a computing resource available to a wide range of people at M.I.T. Throughout the project, the interest and encouragement of researchers within both Real Time Systems and other groups has been a strong motivation for its completion. These researchers have proposed a wide variety of applications for Concert, some of which will be started in the near future. The ma-

jor applications which have been suggested include the following.

- The MuNet The MuNet is a proposed "myriaprocessor" system developed primarily by Bert Halstead [25-28]. He would like to use Concert as a testbed to try out various ideas about message-passing and communication among MuNet nodes.

- 2) Communications During the early phases of the project, the Laboratory for Information and Decision Systems (LIDS) expressed some interest in using Concert to simulate communications networks. They would like to test out routing strategies and communications protocols, and to simulate both existing and proposed network configurations. This would allow them to vary parameters they could not touch on an actual operating network.

- 3) VLSI Current VLSI circuit simulation and layout programs take a great deal of time even on large computers. A multiprocessor system which could take advantage of parallelism could theoretically speed up such programs by orders of magnitude. Rich Zippel would like to use Concert to bring up a circuit simulation program, perhaps a parallel version of SPICE.

- 4) Data Flow Although Concert is not a data flow machine, it could serve as a testbed for programming and architectural concepts during the design of a true data flow multiprocessor [5-7,16,24]. Arvind believes that Concert would be useful in this respect, and has indicated some interest in using the system.

- 5) Parallel Control Flow The control flow approach to multiprocessor programming has some similarities to data flow [19,54]. Tom Sterling is working on the specification of a dispatcher for a parallel control flow multiprocessor system. He will use his dispatcher to control a Concert system and operate it as a parallel control flow machine.

- 6) High-Performance Graphics Bert Halstead will use Concert to implement a high-performance graphics system. He envisions a number of Concert nodes processing graphics commands and filling up a common bitmap in global memory. A custom graphics processor will be built to display the contents of the bitmap memory on a high-resolution monitor.

- 7) Music Synthesis Bert Halstead also has some interest in the use of Concert for high-performance music synthesis. For example, if each Concert node is assigned a voice, the resulting music will be much more complex than a single processor could generate.

- 8) Multiprocessor LISP Bert Halstead and Rich Zippel are planning to bring up a multiprocessor version of LISP to run on Concert. This will be a particularly interesting test of the system in a non-traditional programming environment.

- 9) Electrical Demand Simulation Fred Schweppe and Jim Kirtley of the Electrical Power Systems Engineering Laboratory (EPSEL) are interested in using Concert to simulate electrical energy demand in transmission and distribution systems [34,48-49]. This particular application could prove a best-case test for Concert, since the inherent locality of the simulation algorithms produces low bus contention.

#### 2.4: Design Goals

If Concert is to be useful for all the applications listed in the previous section, it must be flexible as well as easy to use. Specifically, it must support most applications without the need for hardware redesign. Exceptions will be made primarily for reasons of efficiency. For example, a specialized dispatcher will be designed for the parallel control flow machine because a standard Concert node would be too slow. Regardless, it would be possible for a standard node to simulate the control flow dispatcher in software if required.

If Concert is to be a useful tool for the M.I.T. computing community, it must be a reliable, robust system. There are two ways to approach the issue of reliability. The first is that the hardware be physically reliable. Experience with previous projects in the Real Time Systems Group has shown that it is difficult to produce reliable hardware in a university environment. For this reason, the decision was made that Concert

would use off-the-shelf boards and other technology whenever possible. If it achieves its goal of providing off-the-shelf multiprocessing, Concert hardware will be used repeatedly by different groups. It is important that it be able to survive multiple applications without becoming unreliable.

The other main aspect of reliability is software reliability. For the most part this lies outside the scope of this thesis. However, there are some aspects of the design which have been included to help support software robustness, and these are identified as they are encountered.

The basic Concert architecture is designed to support several dozen processing nodes, but the ultimate system will support hundreds. This implies that the hardware must be relatively inexpensive. For example, using fancy floating-point processors for each node would certainly produce a very powerful machine. However, it would be impractical for the scale of research envisioned for the system.

These considerations led to four major goals for the Concert multiprocessor development system: low cost, flexibility, reliability, and ease of use. These goals have permeated every aspect of the hardware (and software) design. The remainder of this thesis describes the attempt to meet these goals. It outlines the Concert system architecture and describes in considerable detail the specific design responsibilities for the thesis project.

#### Chapter 3: The RingBus Architecture

This chapter outlines the RingBus architecture, a scheme for interconnecting processors in a shared-memory multiprocessor system. It presents some background terminology and then describes the architecture in its general form. The specific implementation used in Concert is discussed in Chapter 4.

### 3.1: Dimensions of Multiprocessing

There is a wide variety of ways to look at "multiprocessing." In 1966, Flynn published a classification of computers [20] which is still in use today. He termed the common garden-variety computer a Single Instruction stream, Single Data stream (SISD) machine, because it consists of one control unit whose instructions control a single data path. The majority of computers today are still essentially SISD machines, although a slight degree of parallel processing is accomplished by separate I/O processors and the like.

The only class of computers other than SISD to be implemented widely has been SIMD (Single Instruction, Multiple Data), often called parallel processors. These machines contain a single instruction stream and control unit which manipulates multiple data paths. Some computers in this class are called array processors, [8,11,36,53] since the elements of an array may be fed in parallel into the data units. Associative processors [10,22,59] are also generally considered SIMD machines.

Flynn's MISD category, in which multiple control units manipulate a single data

path, has not turned out to be very useful. Pipelined processors [41,42] are sometimes considered MISD machines, although this is a controversial categorization. Generally, neither SIMD nor MISD machines are considered "true" multiprocessors.

The final, and most complex, class of machines is MIMD, in which multiple intelligent control units manipulate multiple data paths. The most common MIMD configuration is a collection of independent processors, each with its own instruction and data streams. These processors are interconnected in some fashion, so that they can cooperate in the solution of a single problem.

There are two primary subdivisions of MIMD machines. The processors in a loosely-coupled multiprocessor system communicate by sending messages over dedicated links or via a communications network. Such a configuration encourages a message-passing style of programming, in which subtasks execute in parallel on different virtual (and perhaps physical) machines and send commands back and forth. Loosely-coupled systems are sometimes called "multiple computer systems" rather than "multiprocessors" [17-18].

Tightly-coupled systems contains processors which communicate via shared memory, and are generally considered to be "true" multiprocessors. They encourage a programming style in which shared memory locations, often protected by semaphores, are used to pass information between processors and to control program flow.

There are a variety of techniques for interconnecting processors and memory in a tightly-coupled multiprocessor system. The simplest technology is a single shared bus. Tightly-coupled multiprocessors in which accesses to shared memory are made by means of a central system bus are often called *common-bus* systems. This term em-

phasizes the fact that the processors must contend for the bus if they wish to access shared memory. This contention places some inherent limitations on performance.

A variety of approaches has been tried to ease the contention problem. One partial solution is to give each processor its own *local* memory for instructions and private data. Shared, or *global*, memory is used only for shared data structures and for passing information between nodes. If the majority of a processor's accesses are to its own local memory, and this memory is available without contention, the speedup over a system with only global memory can be quite dramatic.

Even with generous local memories, the number of processors which may be placed on a single global bus is small, on the order of a dozen or so. Beyond this point, adding additional nodes does not increase the performance; bus contention negates the parallelism gained by the extra nodes. The simple local/global division is sometimes extended to a hierarchy of buses to ameliorate this problem. In such a system, an attempt is made to place shared data in a location easily accessible to all nodes which need access to it. If this is done properly, the so-called "principle of locality" tends to keep references to global memory as local as possible.

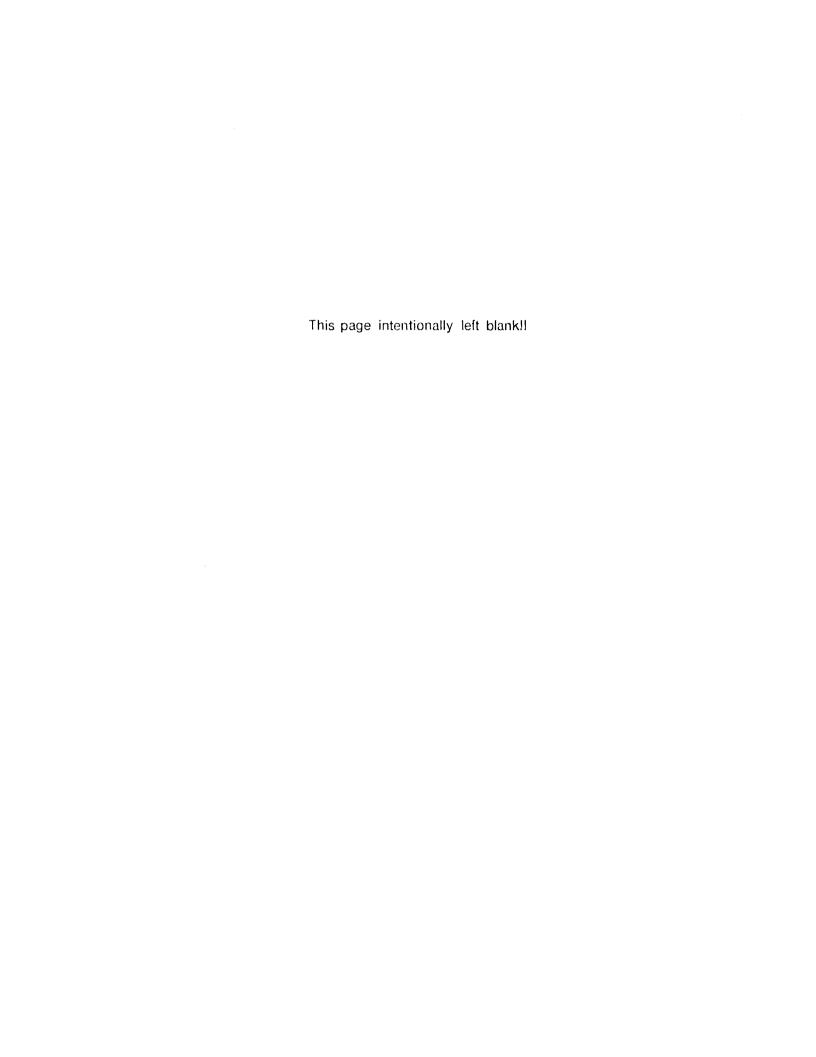

Figure 1 shows a typical multiprocessor system with a hierarchical bus structure. A group of processors on a common bus form a *cluster*. The clusters are themselves connected through address maps along a common system bus. If two tasks frequently access a particular piece of data, an intelligent task and memory allocation scheme might assign the tasks to the nodes labelled *B*1 and *B*2 and place the data in the block of global memory labeled *B*. Since both processors are in the same cluster as the data, they can access it without tying up the system bus. However, if the node la-

belled A3 wishes to access that same data, it must use the system bus to get from its cluster to the desired location in the destination cluster.

Figure 1: Hierarchical Bus Architecture

Even in a hierarchical bus system, contention places limits on the performance. The same constraints that limit the number of processors that may be placed on a single bus apply even more severely to the number of clusters on the system bus. Replicating buses, thereby providing multiple paths between processors and memory modules, is another approach to reducing memory contention [51-52]. The extreme—providing as many paths as processors—is usually implemented by using a crossbar switch or similar technology [39,57,58]. If the switching logic is migrated to the memory modules, the result is a system of processors and multi-port memories, each with as many ports as processors.

The basic Concert system is a tightly-coupled multiprocessor, since it is composed of independent microprocessor nodes which communicate via shared memory. The ul-

timate Concert system will be a loosely-coupled network of tightly-coupled multiprocessors. The system architecture for a basic Concert system uses a hierarchy of buses, but there's an important difference from the organization of Figure 1. The top-level "system" bus is actually formed from a series of bus segments, which may carry out independent accesses to blocks of global memory or may be connected to carry out longer accesses. The remainder of this chapter describes this interconnection architecture.

# 3.2: The General RingBus Architecture

As discussed in the previous section, bus contention is the major limiting factor in the performance of most common-bus multiprocessor systems. Bert Halstead has proposed the RingBus architecture, a processor and memory interconnection scheme which holds the promise of expanding these limits. More importantly, the hardware required to support this architecture is less than that required in many previous tightly-coupled multiprocessor systems. The RingBus architecture was chosen for Concert precisely because of these characteristics.

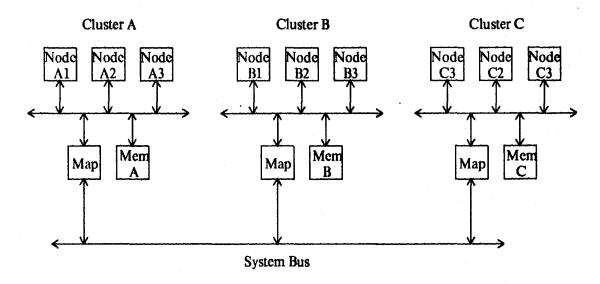

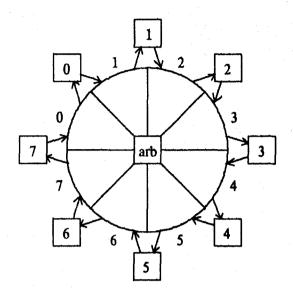

Figure 2 shows a simple picture of a RingBus-based multiprocessor system. The configuration is a *ring* of processing *slices*, interconnected by RingBus *segments*. Each slice contains a block of global memory and, generally, one or more processing *nodes*. A node contains at least a processor, and may also include local memory or other private resources. The RingBus is a single-transaction (read and write) bus which is under the control of a central arbiter.

Figure 2: RingBus Multiprocessor System

The key attribute of the RingBus architecture is that different transactions may be carried out simultaneously on different RingBus segments. Several processors may be carrying out independent accesses to different blocks of global memory in a single ring. All accesses to global memory are under the control of the arbiter, which periodically examines and grants requests from the slices. In general, requests may be granted (and therefore carried out) simultaneously if they do not require any common segments on the RingBus. The arbiter can cause multiple segments to be connected together to perform a single memory access.

The ability to carry out multiple memory accesses simultaneously is what makes the RingBus architecture promising as a multiprocessor interconnection scheme. Most

methods for allowing parallel access to global memory in tightly-coupled multiprocessors require expensive hardware like crossbar switches. The RingBus architecture is a lower-cost alternative which should still yield performance superior to that of common-bus multiprocessors. The idea of using a segmented bus is not original, but it has only rarely been investigated before [4,21].

The next chapter describes the specific implementation of the RingBus architecture which was used as the top-level interconnection scheme for the Concert multiprocessor development system. The design of the hardware to support this architecture comprised the bulk of the thesis project. However, some effort was devoted to investigating the architecture itself, both through analysis and simulation.

#### 3.3: Analysis of the RingBus Architecture

Formal analysis of most aspects of computer architecture is notoriously difficult. Most believable results require some knowledge of the programs which would be run on the machine being simulated. For this reason, software simulation is generally considered more useful than formal models. In the case of the RingBus architecture, both simulation and the design of a working system have been employed. However, some simple analysis was undertaken to investigate useful properties of the architecture. This section outlines some of these properties and describes how they influenced the design.

#### 3.3.1: Major Implementation Options

There are a number of implementation options which affect how much parallelism the RingBus architecture can provide. The most fundamental is whether the RingBus is unidirectional or bidirectional. If it is unidirectional, then address and control lines need to be propagated in only one direction (clockwise or counterclockwise) around the ring. A bidirectional bus allows these lines to propagate in either direction. In either case, the data lines must be bidirectional to support both reads and writes or two sets of unidirectional data lines must be provided.

The choice of directionality on the RingBus is not trivial. A unidirectional bus requires a minimum of hardware, but places some inherent limitations on performance. For example, the worst-case access of a processor to global memory in the slice "behind" it requires the entire RingBus for completion. The worst-case access on a bidirectional RingBus takes only about half of the segments, but more hardware is required to support the bidirectionality. In addition, the arbiter has to be more clever if it is to take advantage of the bidirectional capability.

Another factor which affects the performance of the architecture is the degree of parallelism in each slice. For example, a slice may allow an incoming request on a RingBus segment to access its global memory at the same time a request from a processor within the slice is being propagated out along the other RingBus segment. Again, the arbiter needs to know if such parallelism exists and how best to exploit it.

The design options for the RingBus directionality and the parallelism in each slice are discussed in detail in Chapter 5. The two primary issues involved are the amount of hardware required in the slice and the time required by the arbiter to grant a re-

The Design of a Multiprocessor Development System

quest. Determining the tradeoffs between these costs and the parallelism on the Ringbus was a major part of the design effort.

# 3.3.2: Requesting and Granting

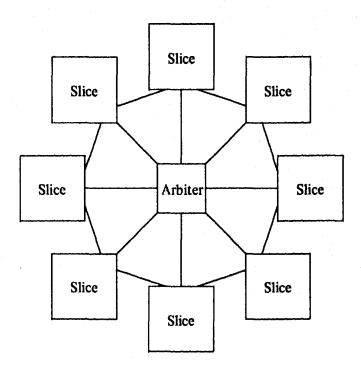

The problem of how to identify simultaneously grantable requests is a fundamental one in a RingBus-based system. The first part of this task is to determine the resources required to carry out a particular access. These requirements may be simply expressed in the Segment Needed List (SNL), which identifies the RingBus segments needed to complete an access. Consider the eight-slice ring shown in Figure 3, in which slices and segments are numbered in order starting at an arbitrary point. Suppose that the following requests are made to the arbiter with no accesses in progress and no requests pending:

The format for the requests is simple;  $S \rightarrow D$  is a request to the arbiter from Slice S for access to global resources in Slice D. Given this set of requests, the arbiter must then decide which requests to grant and which to defer. Table 1 expresses the same set of requests in a slightly different format which anticipates the design of the interface between the arbiter and the slices. The REQ line from a slice is asserted if it is making a request, and the DST lines identify the destination slice for a request.

In general, the segments needed for a request depend upon the direction of the access on the RingBus. Table 2 shows the SNLs for both clockwise and counterclockwise accesses for the requests of Table 1. If the RingBus is unidirectional, then all requests propagate in one direction around the ring. If the RingBus is bidirectional, then

Figure 3: Ring with Slice and Segment Numbers

| Source | REQ | DST |

|--------|-----|-----|

| 0      | 0   | Х   |

| 1      | 1   | 3   |

| 2      | 1   | 4   |

| 3      | 0   | ×   |

| 4      | 1   | 7   |

| 5      | 1   | 5   |

| 6      | 1   | 3   |

| 7      | 0   | X   |

Table 1: Sample Round of Requests

a request may propagate in either direction. The directionality of the ring in Figure 3 is intentionally left unspecified.

The SNL may be translated into a binary vector simply by placing a "1" in a bit if the segment is required, or a "0" if not. For example, the SNL for a clockwise access

| segment | Clockwise Access |   |   |         |          |   |   | Counterclockwise Access |   |          |   |   |   |   |   |   |

|---------|------------------|---|---|---------|----------|---|---|-------------------------|---|----------|---|---|---|---|---|---|

| request | 0                | 1 | 2 | 3       | 4        | 5 | 6 | 7                       | 0 | 1        | 2 | 3 | 4 | 5 | 6 | 7 |

| 1→3     |                  | х | х | X       |          |   |   |                         | х | X        |   | × | х | x | x | X |

| 2-+4    |                  |   |   | X       | х        | Х |   |                         | х | х        | X |   | х | х | Х | × |

| 4→7     | 1                |   |   | <b></b> | X        | X | X | х                       | X | X        | X | X | X |   |   | × |

| 5→5     |                  |   |   |         | <u> </u> | Х |   |                         |   | <u> </u> |   | 1 |   | × |   |   |

| 6→4     | X                | X | х | х       | Х        |   | X | Х                       |   |          |   |   | X | х | X |   |

Table 2: Segment Needed Lists for Requests of Table 1

for the request 1→3 is "01110000." Given the SNLs for two requests, it is a simple matter to determine if they are simultaneously grantable. Two global accesses may be carried out simultaneously if they do not require any common RingBus segments. Thus, two requests may be granted concurrently if the AND of their two SNLs has no bits set.

In general, when the arbiter is deciding whether to grant a request there are some number of accesses already in progress. Therefore, it is necessary to be able to efficiently determine if a request conflicts with any of a number of requests already granted or in progress. This also turns out to be simple. A composite list of segments in use thus far may be maintained, and the request under consideration is ANDed with this list. Each time a new request is granted, its SNL is ORed with the list to produce a new composite list.

#### 3.3.3: The Role of the Arbiter

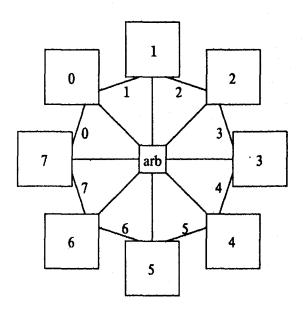

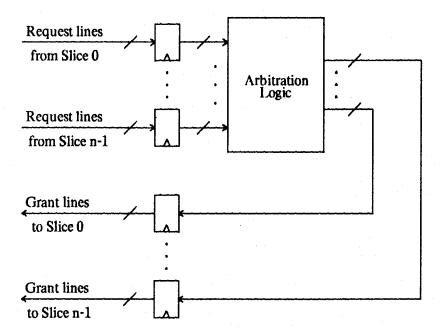

The arbiter is responsible for controlling all accesses to global memory on the RingBus. It takes as input request lines from the slices, and sends back grant signals which control the flow of information on the RingBus segments. The first cut at the arbiter is a block of combinational logic mapping request inputs to grant outputs. The arbiter's inputs must remain stable long enough for it to make a decision; likewise its outputs to the slices must remain stable while it is making decisions. Thus, both the request inputs and grant outputs must be latched. Figure 4 shows a simple model for such an arbiter in ring with n slices.

Figure 4: Combinational Model of the Arbiter

The arbiter latches its inputs and outputs on a synchronous clock. The time between clock pulses is the arbiter cycle, which is determined by the latency of the arbitration logic. Each time a cycle begins, a round of requests from the slices is latched in. At the end of the cycle, the lines indicating which of the requests have been granted are latched and sent back to the slices.

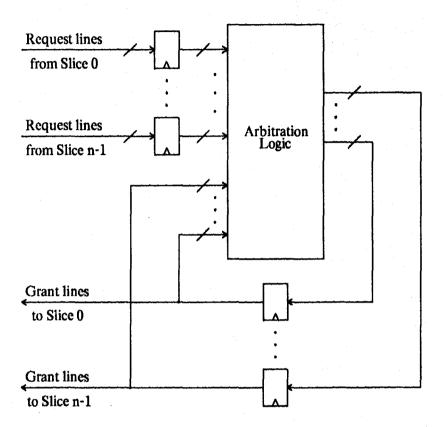

Unfortunately, the simple model of Figure 4 is insufficient on two counts. First, the arbiter must have some sort of state to record which requests are currently in progress. Since a RingBus access may take an arbitrary number of arbiter cycles to complete, the arbiter must insure that once a request is granted it remains granted until completion. Since the grant signals sent to the slices must be latched anyway, the obvious way to insure this is to feed them back into the arbiter. Figure 5 shows the resulting finite-state machine implementation of the arbiter.

The arbiter implementation of Figure 5, while more realistic than a totally combinational version, still lacks one important property. For the arbiter to be useful in a real system, it must eventually grant all requests. Some of the requests in a given round may require common RingBus segments. Thus, in general, not all requests can be granted in a single arbiter cycle. Any ungranted requests will still be pending on subsequent arbiter cycles. It is possible that whatever method the arbiter uses to select among conflicting requests will result in some requests never being granted.

This problem may be rectified by maintaining some state in the arbiter to insure that pending requests are eventually granted. This is the simplest form of fairness for an arbitration scheme; a request can never be locked out forever. A more strict definition of fairness in the RingBus architecture requires that all nodes have an equal

Figure 5: Finite-State Machine Model of the Arbiter

chance for global memory access. If all slices contain an equal number of nodes, this is equivalent to the requirement that all slices have an equal chance at global resources.

If the slices have different numbers of nodes, the problem of guaranteeing fairness becomes more difficult. In this case, the arbiter needs to know the exact configuration of the system, including the number of nodes in each slice. All arbitration schemes discussed in this chapter consider all slices equivalent. Thus, they do not guarantee

that all nodes have an equal chance for access to global resources.

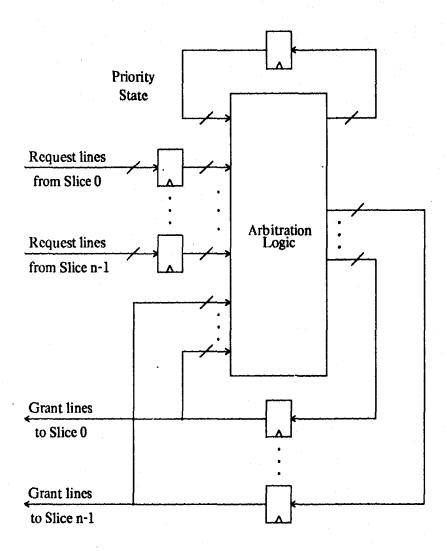

The next section discusses some schemes to enforce a priority order on the requests. Such an order may be used to insure that a pending request is eventually granted by assigning it a higher priority than incoming new requests. The finite-state machine model of the arbiter is still valid, but it must incorporate some additional state to insure fairness. Figure 6 shows a modified model which includes some priority state.

# 3.3.4: Arbiter Priority Schemes

A priority ordering on the requests to the RingBus arbiter is required to insure that all requests will eventually be granted. For a ring of n slices, no more than n requests may be made to the arbiter at any one time. Thus, only n priority levels are required. If each priority level can contain only one request, then there are n! possible priority orderings. If more than one request can have the same priority, there are  $n^n$  combinations.

There are two fundamentally different ways for the arbiter to order the requests. The first approach is a history priority scheme, in which requests are ordered by age. There are several possible implementations to support such a scheme. For example, the arbiter might include a "history counter" for each source. The priority ordering may be determined from the values of these counters by a comparison tree or similar hardware. A new request starts at the lowest priority, and its priority is increased by incrementing its counter as long as it is pending. Requests of the same age may have

Figure 6: Model of Arbiter with Priority

the same priority; in such a case, the arbiter must decide among them arbitrarily.

Since the history counters need to hold one of *n* possible values, the number of bits required is the logarithm of the number of slices. The issue of when to increment the counters is not as simple as it might seem. Since each request may take an arbitrary number of arbiter cycles to complete, the arbiter may have periods of arbitrarily

many cycles in which it can grant no new requests. If the history counters are incremented each arbiter cycle, they can eventually overflow and older requests can end up with lower priority than newer requests.

A better, but more difficult, approach is to increment the history counters up to the maximum value to fill in "holes" in the priority ordering. Once a request has reached the top priority, it remains there until granted. If only one request is desired at each priority level, then the ordering of requests which arrive in the same cycle may be chosen arbitrarily. If multiple requests may have the same priority, a curious result ensues. As long as two requests from different cycles always have different priorities, then the number of requests possible at priority level p in a ring of n slices is n-p. This assumes that the priority p ranges from 0 to n-1, with n-1 being the top priority.

The "hole-filling" scheme suggests an alternative implementation for history priority

— a queue for the requests. The queue needs one stage for each slice in the ring.

Presumably the stages would be completely ordered, so that each stage represents a fixed priority level and contains at most one request. Each time a new request arrives, the earlier requests are pushed up and the new request is added to the bottom.

There are several serious problems with this approach. As discussed in the next section, there are circumstances in which it is valid to grant a request even if requests of higher priority remain ungranted. Once such requests complete, "holes" are left in the request queue. If the queue only has as many elements as slices, it is necessary to fill the holes in order to fit all the requests in. This requires the ability to selectively shift elements in the queue, which is not provided by many possible implementations.

If the elements of the queue are available in parallel, it is possible to simultaneous-

ly examine requests of different priority levels. If not, then a shift must be performed to present each request in turn in priority order. In a ring with n slices, as many as n requests may be granted in a single arbiter cycle. Thus, it may be necessary to shift n times. Similarly, as many as n new requests may occur in a single cycle. Thus, it is necessary either to shift as many as n times each cycle or to have some way of loading the queue in parallel.

The amount of hardware necessary to implement the history counter scheme is far from trivial, since it involves comparison hardware to determine the priority ordering. On the other hand, the queue implementation requires some clever hardware and may exact a time penalty for the shifting around of requests in the queue.

A history priority scheme has the advantage that requests are granted by age, a reasonable criterion for deciding conflicts. The other major class of methods to order the requests to the arbiter involves priority schemes which do not rely on the nature of the requests themselves. A *fixed priority* ordering is one such method, but it does not give all slices an equal access to global resources.

One scheme commonly used in bus arbitration is *rotating priority*. This is basically a fixed priority ordering which rotates among the slices. Such an approach works with the RingBus as well. The simplest form just assigns the top priority slot to a different slice each cycle. For example, consider again an eight-segment RingBus with the slices numbered from 0 to 7. Table 3 shows the priority orderings for nine consecutive arbiter cycles. From this representation, it is clear how the term *rotating* arose. Unlike some of the history schemes, each priority level has exactly one request at a time.

| Priority | Slice Priorities for each Cycle |     |     |     |     |     |     |     |     |

|----------|---------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| Level    | n                               | n+1 | n+2 | n+3 | n+4 | n+5 | n+6 | n+7 | n+8 |

| 0 (low)  | 3                               | 4   | 5   | 6   | 7   | 0   | 1   | 2   | 3   |

| 1        | 4                               | 5   | 6   | 7   | 0   | 1   | 2   | 3   | 4   |

| 2        | 5                               | 6   | 7   | 0   | 1   | 2   | 3   | 4   | 5   |

| 3        | 6                               | 7   | 0   | 1   | 2   | 3   | 4   | 5   | 6   |

| 4        | 7                               | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

| 5        | 0                               | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 0   |

| 6        | 1                               | 2   | 3   | 4   | 5   | 6   | 7   | 0   | 1   |

| 7 (high) | 2                               | 3   | 4   | 5   | 6   | 7   | 0   | 1   | 2   |

Table 3: Nine Consecutive Cycles of Rotating Priority

The implementation for rotating priority is extremely simple — a counter which identifies the current top priority slice and which is incremented each cycle. In an n-slice ring there are only n possible priority orderings, so that the number of bits in the counter is  $\log_2 n$ . Unfortunately, this simple scheme will not work for the RingBus. Unless a request is held at the top priority until it is granted, it may be superseded by a new request. It is possible that a request is not granted (because of conflicts with accesses already in progress) every time it reaches top priority, and is therefore locked out forever.

A more sophisticated version of rotating priority solves this problem. A request is held at the top priority until it is granted. Once the request is granted, the priority is rotated so that the next slice which has a pending ungranted request gets top priority. The hardware to implement such a scheme is a little more substantial. Instead of a simple "top priority" counter which gets incremented each cycle, more complicated logic is needed to determine the next value of the counter based on the its current value and the current ungranted requests.

#### 3.3.5: Arbitration Algorithms

Before attempting to design the arbiter, some effort was spent in examining some possible arbitration algorithms to better understand the function which has to be performed. Assuming some sort of priority ordering on the requests, the basic algorithm is quite simple — try to grant the requests in priority order. However, there are several factors to consider.

The first point is that requests may take an arbitrary number of arbiter cycles to complete. This requires that any request, once granted, *must* be allowed to complete without interruption. In terms of the arbiter, this implies that all requests which were granted on a previous cycle and which are still active must be granted again. Algorithm 1 expresses this procedure in a simple Pascal-like language. All algorithms in this section use this same language.

```

procedure UPDATE_GRANT;

I update the grant list

integer

! current slice being considered

constant

NSL:

! number of slices, numbered 0 ... NSL-1

boolean array REQ[NSL];

I true if the slice has a request pending

boolean array GRANT[NSL];

! true if slice's request has been granted

! update the grant list with those requests granted

! but not yet complete

for S := 0 to (NSL-1) step 1 do

GRANT[S] = GRANT[S] and REQ[S];

}

```

Algorithm 1: Updating the Grant List

The GRANT array is the structure that is modified by the arbitration algorithms. In hardware terms, the array can be thought of as the GRANT lines which feed into the output latches. At the end of the arbiter cycle, the GRANT values are latched into the register and sent to the slices. Likewise the value of the REQ array may be thought of as the latched values of the request lines from the slices. An access is assumed complete once its request line has dropped. Thus, at the start of an arbiter cycle, a request is still in progress if its bits in the GRANT and REQ arrays are both set.

Once the *GRANT* array has been updated, the actual arbitration process can occur. The core of the decision whether or not to grant a request is the SNL abstraction discussed earlier in this chapter. Two requests may be granted simultaneously if they require no common RingBus segments. Algorithm 2 is a simple function for identifying conflicts among requests. It takes as inputs two slice numbers and returns *true* if the two requests may be granted simultaneously and *false* if they may not. It determines this by comparing the SNLs of the two requests. It uses an unspecified function *SNL* which takes a slice number and a segment number and returns *true* just in case the specified request needs the specified segment for completion.

There is one other auxiliary routine which is used by the arbitration algorithms. This procedure, *UPDATE\_PRI*, updates the priority ordering of the requests at the end of an arbiter cycle. A detailed priority update algorithm is not given because it is so hardware-dependent and because there are so many possible schemes. The exact action taken by *UPDATE\_PRI* depends upon the particular priority scheme and hardware implementation selected. For example, the rotating priority update algorithm keeps the priority order the same if the top priority request is ungranted. If it is granted, then the

```

function CONFLICT(S1, S2);

I returns true if requests of slices

I S1 and S2 require any common segments

integer

S1, S2;

boolean

CONFLICT:

! returns true if request of slice SL needs

extern function

SNL(SL,SG);

! segment SG, else false

! number of slices, numbered 0 ... NSL-1

NSL:

constant

I current segment being considered

integer

SEG:

! set true once a conflict is found

boolean

CONFL:

CONFL := false;

for SEG := 0 to (NSL-1) step 1 do

CONFL := CONFL or (SNL(S1,SEG) and SNL(S2,SEG));

return (CONFL);

}

```

Algorithm 2: Identifying Conflicting Requests

priority is rotated to give the highest-priority ungranted request top priority for the next arbiter cycle. If no requests remain ungranted, the priority might be rotated by one.

The arbitration algorithms assume only that some sort of priority order has been established. This order is represented by the array *PRI*, which holds the priority value for each of the *NSL* slices in the ring. Each priority value is between 0 and *NSL*-1, with *NSL*-1 being the highest priority. The algorithms allow for arbitrary priority orderings and permit multiple requests at each priority level. They support any of the priority schemes discussed in the last section, ranging from rotating priority to history counters.

There are two fundamental goals for the arbitration algorithm, and for the arbiter itself. It should be fair, giving all slices an equal shot at the RingBus and the global resources. Of course, this also means that all requests should be eventually granted.

It should also try to exploit the maximum parallelism on the RingBus by granting as many requests as possible simultaneously. There are several important variations in the arbitration algorithm which affects its compliance with these design goals. Algorithm 3 is the most straightforward arbitration scheme. It simply iterates down through the priority levels, attempting to grant all requests at each level. In this manner, requests of higher priority get a chance to be granted before requests of lower priority.

There are several important points to note about Algorithm 3. The first is that it is general enough to work with any of the three priority schemes presented in the last section. The appropriate version of *UPDATE\_PRI* is chosen to reflect the priority scheme. If a rotating priority scheme is used, the algorithm may be optimized to recognize that there is exactly one request at each priority level. The algorithm also contains calls to *UPDATE\_GRANT* and *CONFLICT*, as defined earlier.

Although Algorithm 3 appears to be a perfectly reasonable arbitration method, it does not guarantee that all requests are eventually granted. The problem arises when a high priority request does not get granted because of a conflict with a request already in progress. If this happens, lower priority requests may be granted in that same cycle. However, it is possible for the high priority request to get locked out forever if lower priority requests which conflict with it are continually granted. The obvious solution to the problem is shown in Algorithm 4, which stops granting requests as soon as a conflict is found.

Algorithm 4 is termed the *limited arbitration scheme* because it grants fewer requests than does Algorithm 3. This means that it allows fewer simultaneous accesses on the RingBus, and some of the advantage of the architecture is lost. Fortunately,

there is a third choice which exploits more parallelism than Algorithm 4 yet insures that all requests will be eventually granted. This approach, the full arbitration scheme, is shown in Algorithm 5.

The key is that the problem with Algorithm 3 arises only when it grants lower priority requests which conflict with ungranted higher priority requests. Algorithm 5 solves this problem by granting a request only if it does not conflict with either a request already granted or an ungranted higher priority request. As usual, it checks for conflicts by comparing the SNLs of the requests.

All three arbitration algorithms share a fundamental common trait — they make only one pass through the requests. It is possible to imagine algorithms which make multiple passes through the requests, trying to achieve the maximum parallelism on the RingBus. Such schemes require some sort of figure of merit to compare different sets of grants for the same round of requests. Among the metrics which might be considered by a multiple-pass arbiter are:

- 1) Granting each request in as short a time as possible.

- 2) Granting as many requests as possible simultaneously.

- 3) Using as many RingBus segments as possible simultaneously.

- 4) Giving preference to "short" requests, where the length of a request is defined as the number of RingBus segments in its SNL.

- Giving preference to "long" requests.

- Considering both directions on a bidirectional RingBus for each request.

```

procedure ARBITRATE:

! perform the arbitration

integer

S;

I current slice being considered

C;

! competing slice being considered

integer

P:

integer

! current priority being considered

boolean

CONFOUND:

I true if conflict has been found

boolean array REQ[NSL]:

I true if the slice has a request pending

boolean array GRANT[NSL];

I true if slice's request has been granted

integer array PRI[NSL];

! priority of slice's request (ranges

! between 0 and NSL-1)

{

UPDATE_GRANT:

I work down through priority levels

for P := (NSL-1) to 0 step -1 do

! iterate over the slices

for S := 0 to (NSL-1) step 1 do

if (PRI[S] = P) and REQ[S] and not(GRANT[S])

I if the request is the right priority

I and not yet granted, try to grant it

CONFOUND := false;

for C := 0 to (NSL-1) step 1 do

! check for conflicts with requests

! already in progress

if GRANT[C] then

if CONFLICT[S,C] then

CONFOUND := true;

exitloop(C);

I if no conflict was found, grant request

if not(CONFOUND) then GRANT[S] := true;

UPDATE_PRI:

}

```

Algorithm 3: Initial Arbitration Scheme

```

procedure ARBITRATE:

! perform the arbitration

integer

S:

I current slice being considered

C;

integer

! competing slice being considered

P:

integer

I current priority being considered

boolean array REQ[NSL];

! true if the slice has a request pending

boolean array GRANT[NSL];

! true if slice's request has been granted

integer array PRI[NSL];

! priority of slice's request (ranges

! between 0 and NSL-1)

{

UPDATE_GRANT:

I work down through priority levels

for P := (NSL-1) to 0 step -1 do

! iterate over the slices

for S := 0 to (NSL-1) step 1 do

if (PRI[S] = P) and REQ[S] and not(GRANT[S]) then

! if the request is the right priority

! not yet granted, try to grant it

for C := 0 to (NSL-1) step 1 do

! check for conflicts with requests

! already in progress

if GRANT[C] then

if CONFLICT[S,C] then

exitloop(P);

I if no conflict was found, grant request

GRANT[S] := true;

UPDATE_PRI:

}

```

Algorithm 4: Limited Arbitration Scheme

```

procedure ARBITRATE;

! perform the arbitration

integer

! current slice being considered

S;

C;

integer

! competing slice being considered

integer

P:

I current priority being considered

boolean

CONFOUND:

! true if conflict has been found

I true if the slice has a request pending

boolean array REQ[NSL]:

boolean array GRANT[NSL];

I true if slice's request has been granted

integer array PRI[NSL];

! priority of slice's request (ranges

! between 0 and NSL-1)

{

UPDATE_GRANT;

! work down through priority levels

for P := (NSL-1) to 0 step -1 do

! iterate over the slices

for S := 0 to (NSL-1) step 1 do

if (PRI[S] = P) and REQ[S] and not(GRANT[S]) then

{

! if the request is the right priority

! and not yet granted, try to grant it

CONFOUND := false;

for C := 0 to (NSL-1) step 1 do

I check for conflicts with requests in progress

! or ungranted requests of higher priority

if GRANT[C] or (REQ[C] and (PRI[C]>PRI[S])) then

if CONFLICT[S,C] then

{

CONFOUND := true;

exitloop(C);

! if no conflict was found, grant request

if not(CONFOUND) then GRANT[S] := true;

UPDATE_PRI:

}

```

Algorithm 5: Full Arbitration Scheme

Multiple-pass arbitration algorithms are not considered in this thesis. The primary reason for this is the practical difficulty in implementing such an approach in hardware. Fundamentally, considering different possibilities for the same round of requests requires either parallel hardware or serial passes with the same hardware. Since the RingBus was investigated in terms of its usefulness for Concert, both implementations were judged unacceptably costly.

### 3.4: Simulation of the RingBus Architecture

Simulation has long been a useful tool in the design of multi-level memory systems, protocols, and other aspects of computer architecture. Likewise, it can have considerable impact on the detailed definition and implementation of a RingBus-based multiprocessor system. Simulation can help to choose the arbitration and priority schemes and to assess the impact on performance of some possible variations in the RingBus architecture. The thesis project included some simulation to help understand these issues for the Concert RingBus implementation.

An arbiter simulator was written in the language C [35] under the UNIX [55] operating system to test the effects of some different implementations of the RingBus architecture. Three main parameters were varied — the directionality of the RingBus, the scheme used to enforce priority, and the actual arbitration algorithm. The program was designed in a modular fashion to support these variations.

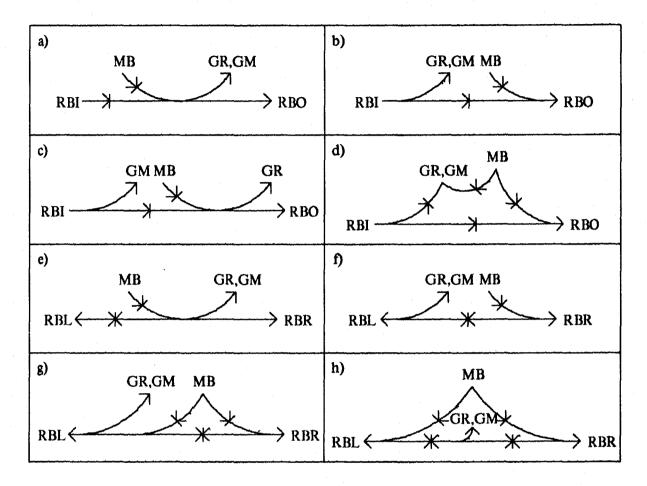

The simulator supports either a unidirectional or bidirectional RingBus. The unidirectional case allows some parallelism within the slices; an access to the resources in a slice can be in progress at the same time that a request from a node within the slice is being sent out to another slice. The bidirectional RingBus supports this same type of parallelism in one direction, but not in the other. Complete details of the two options are given in Chapter 5; a model for the unidirectional case is shown in Figure 19b and a model for the bidirectional bus in Figure 19f. From the arbiter standpoint, the difference between the two is reflected purely in the SNLs generated for the requests.

The simulator supports two priority schemes. The first is a history priority scheme which allows only one request per priority level and shifts requests to fill up holes. The other is a rotating priority scheme which makes the highest priority ungranted request the top priority request for the next cycle. In addition, two different arbitration algorithms are also allowed. The *limited* arbitration scheme is modelled after Algorithm 4, since it stops granting requests once it encounters one it can't grant. The *full* arbitration scheme grants any requests which don't conflict with higher priority requests or requests already granted, and thus follows Algorithm 5. The simple rotating priority scheme and the arbitration scheme of Algorithm 3 were not supported because, as explained earlier, they can result in a request being locked out forever.

A simple random number generator program was used to generate lists of requests to send to the arbiter. It uses a distribution in which accesses from a given slice to other slices vary as an inverse exponential based upon the distance between the slices. This distribution was chosen in an attempt to model the pattern of accesses which might be found in an actual RingBus system if locality was considered in the allocation of global data to global memory blocks in the slices. The distribution was also chosen to reflect the Concert RingBus implementation. The majority of the requests

are assumed to be to global memory within the same slice; in Concert such an access does not require a request to the arbiter or the use of any RingBus segments. The least likely access is thus to the same slice, which happens only on an access to global control registers.

The request sequences generated by this method are probably not a realistic model of the memory accesses in the operating Concert system. Regardless, it is interesting to compare the results of variations in the simulator options for a single sequence of requests. Table 4 summarizes two such experiments. The first set of figures was generated by a sequence of 500 requests from each slice. About half of these requests are *null*, corresponding to memory accesses within the slice. The remainder are requests to another slice. The distribution for the requests favors the bidirectional RingBus, since it makes accesses to slices at the same distance in either direction around the bus equally likely. The same sequence was run through the arbiter simulator eight times, over all variations in the options.

The second set of figures in Table 4 was generated by a different sequence of 500 requests from each slice. The distribution for this sequence favored the unidirectional RingBus, since it considers only one direction. In other words, an access from a slice to the one "behind" it on the RingBus is very unlikely. The same eight combinations of options were tried.

Table 4 gives four statistics for each of the simulator runs.  $t_T$  is the total number of arbiter cycles required to grant all the requests. The average number of cycles a request had to wait before being granted is shown as  $t_{WM}$ .  $r_M$  is the average number of requests made to the arbiter each cycle. The parallelism on the RingBus is

| RingBus | Arbiter | Priority |                | Bidirectional Bias |                |                |      | Unidirectional Bias |                 |                |                |      |

|---------|---------|----------|----------------|--------------------|----------------|----------------|------|---------------------|-----------------|----------------|----------------|------|

| Direct. | Scheme  | Scheme   | t <sub>T</sub> | <sup>t</sup> wm    | r <sub>M</sub> | a <sub>M</sub> | SM   | t <sub>T</sub>      | <sup>t</sup> wm | r <sub>M</sub> | a <sub>M</sub> | SM   |

| Unidir. | Limited | History  | 2568           | 5.29               | 6.05           | 1.94           | 4.50 | 2303                | 4.21            | 5.81           | 2.17           | 4.25 |

| Unidir. | Limited | Rotating | 2765           | 6.11               | 6.21           | 1.80           | 4.18 | 2584                | 5.47            | 6.15           | 1.93           | 3.79 |

| Unidir. | Full    | History  | 2344           | 4.46               | 5.92           | 2.13           | 4.93 | 2013                | 3.16            | 5.61           | 2.48           | 4.87 |

| Unidir. | Full    | Rotating | 2415           | 4.81               | 6.04           | 2.07           | 4.78 | 2149                | 3.82            | 5.86           | 2.32           | 4.56 |

| Bidir.  | Limited | History  | 2205           | 3.86               | 5.75           | 2.26           | 4.10 | 2265                | 4.08            | 5.80           | 2.20           | 4.09 |

| Bidir.  | Limited | Rotating | 2351           | 4.66               | 6.07           | 2.12           | 3.85 | 2461                | 5.08            | 6.15           | 2.03           | 3.77 |

| Bidir.  | Full    | History  | 1874           | 2.52               | 5.34           | 2.66           | 4.82 | 1927                | 2.75            | 5.44           | 2.59           | 4.81 |

| Bidir.  | Full    | Rotating | 1879           | 2.72               | 5.54           | 2.66           | 4.81 | 2020                | 3.24            | 5.67           | 2.47           | 4.59 |

$t_T$  = Total cycles to grant all requests

$t_{WM}$  = Average cycles waited between request and grant

$r_M$  = Average requests made each cycle

$a_M$  = Average accesses in progress each cycle

$s_M$  = Average number of segments in use each cycle

Table 4: RingBus Arbiter Simulation Results for Two Sequences of 500 Requests per Slice

represented by  $a_M$  and  $s_M$ , which list the average number of accesses taking place and the average number of segments in use on the RingBus each cycle.  $a_M$  is equivalent to the average number of requests granted each cycle.

Each sequence has 1994 active (non-null) requests. Once granted, each request takes one or two cycles to complete. The simulator inserts a null request between any two consecutive active requests from a single slice, since reading a null request for a cycle is the only way the arbiter can tell that the previous request is done.

For comparison purposes, a program was also written to simulate the arbiter for a multiprocessor system in which all the slices are connected along a single common bus. An idle cycle is required between any two accesses to signal the end of a re-

quest and to simulate the bus exchange time. The same two priority schemes were used to perform the arbitration, and simulation runs were made with both priority schemes for the same two request sequences which produced Table 4. The result for the common bus simulator is shown in Table 5.

| Priority |                | Bidire          | ectional       | Bias           |       |                | Unidi | rectiona       | Bias           |                |

|----------|----------------|-----------------|----------------|----------------|-------|----------------|-------|----------------|----------------|----------------|

| Scheme   | t <sub>T</sub> | <sup>t</sup> wm | <sup>r</sup> M | a <sub>M</sub> | SM    | t <sub>T</sub> | twm   | <sup>r</sup> M | <sup>a</sup> M | s <sub>M</sub> |

| History  | 5018           | 15.0            | 6.96           | 0.994          | 0.994 | 5018           | 15.0  | 6.96           | 0.994          | 0.994          |

| Rotating | 5020           | 15.0            | 6.95           | 0.994          | 0.994 | 5020           | 15.0  | 6.95           | 0.994          | 0.994          |

$t_T$  = Total cycles to grant all requests

t<sub>WM</sub> = Average cycles waited by request before grant

$r_M$  = Average requests made each cycle

$a_M$  = Average accesses in progress each cycle

$s_M$  = Average number of segments in use each cycle

Table 5: Common Bus Arbiter Simulation Results for Two Sequences of 500 Requests per Slice

In a common-bus system, there is only one bus segment and only one request can be granted at a time, so  $a_M$  and  $s_M$  have a maximum value of one. Idle bus cycles reduce these numbers, although they remain identical. As it turned out, the request sequences produced a few idle cycles, and so the values of  $a_M$  and  $s_M$  are slightly less than unity. The statistics for both the unidirectional and bidirectional biased sequences are identical; the only difference between them is the destinations, which don't matter to the arbiter of a common bus.

In addition to computing statistics based on rounds of arbitration, the simulator also displays a crude representation of the RingBus, showing the accesses currently in

progress and the segments currently in use. This display capability is due to the efforts of Jim Troisi, and provides an easy way to observe the activity in the ring.

It is unwise to draw any quantitative conclusions on the basis of the experiments with the arbiter simulator. However, the results do give a feel for the advantage gained by a bidirectional RingBus over a unidirectional one, and the variations caused by the different arbitration algorithms and priority schemes. More credible results would require more extensive simulations, preferably based on sequences of memory accesses culled from programs written for a shared-memory multiprocessor system. Such results could undoubtedly be used to help make design decisions for future RingBus implementations.

# Chapter 4: The Concert System Architecture

This chapter outlines the implementation of the RingBus architecture which was incorporated in the Concert multiprocessor development system. It includes a discussion of the Concert address space and the terminology which is used in the remainder of the thesis. The detailed design of two custom hardware modules is discussed in the following chapters.

## 4.1: The Concert RingBus Implementation

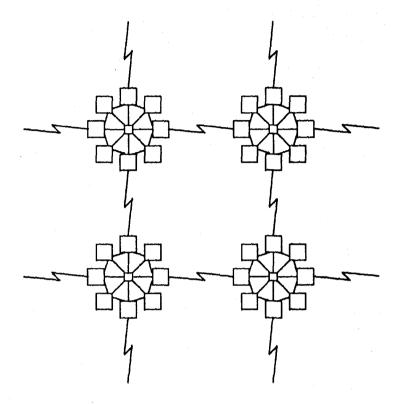

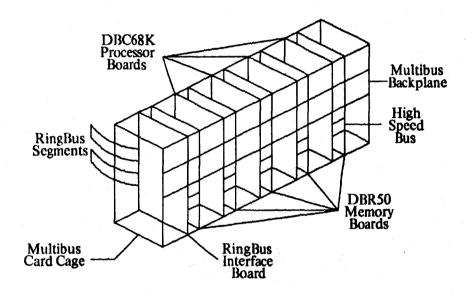

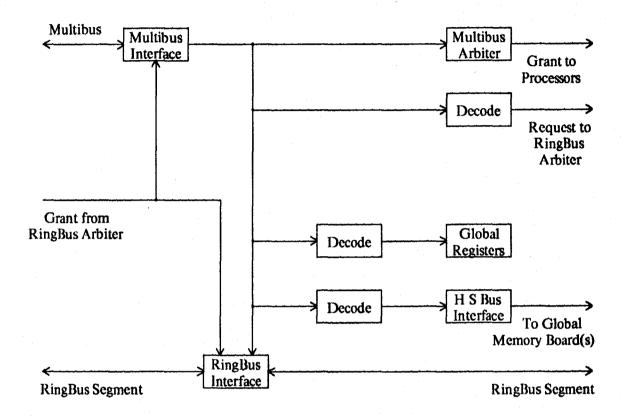

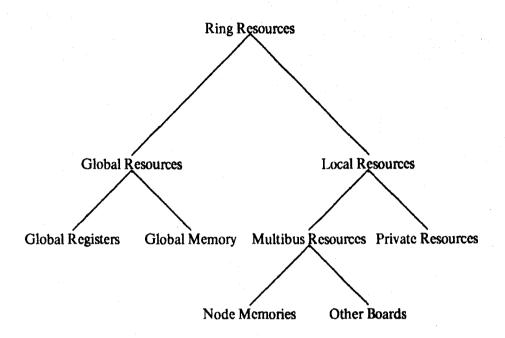

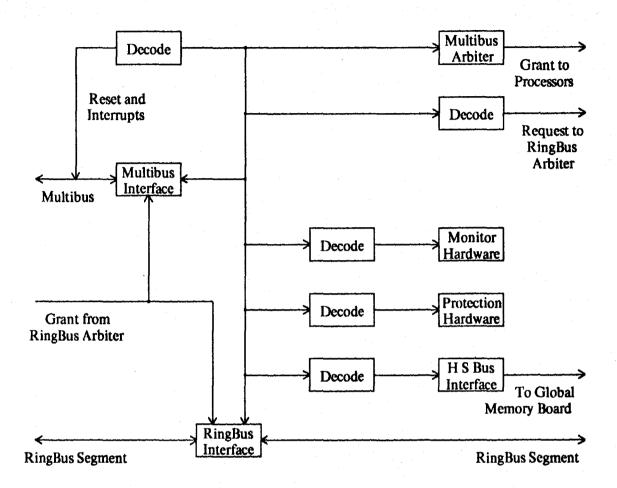

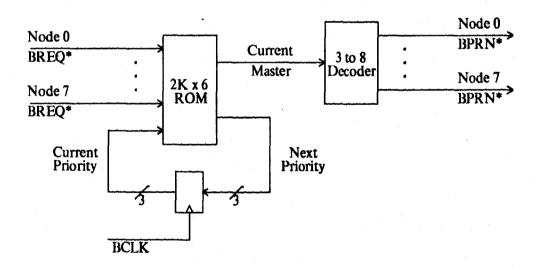

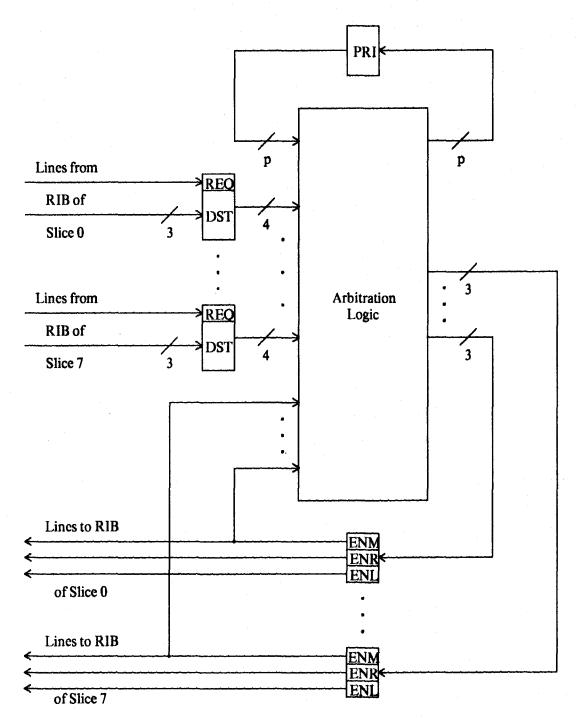

A complete Concert system consists of some number of RingBus rings, interconnected by dedicated serial or parallel lines, as shown in Figure 7. The result is a loosely-coupled network of tightly-coupled multiprocessors. The initial hardware and software design has concentrated on the construction of a single ring, while providing the hooks for an eventual multi-ring system. Most of the discussion in the remainder of the thesis concerns a Concert system of only one ring, although mention is made of some important points about larger systems.

The Concert architecture can best be understood in terms of its hierarchical structure. The computing power of the system lies in processing *nodes*, each containing a processor and, possibly, local memory. Several of these nodes, global memory boards, and a RingBus interface board comprise a RingBus *slice*, which is physically housed in a card cage. Multiple cages connected together by RingBus *segments* and a RingBus arbiter form a *ring*. Finally, one or more rings may be interconnected to form a Con-

Figure 7: Concert System

cert system. Each of the levels in this hierarchy is outlined briefly.

## 4.1.1: The Node

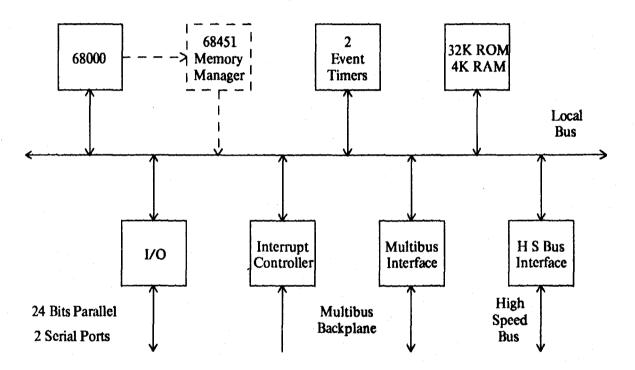

A Concert processing node contains at least a processor, and generally some memory and I/O ports as well. The Concert prototype uses a Microbar DBC68K processor board [13] and a Microbar DBR50 memory board [15] for each node. Figure 8 shows the contents of a DBC68K board. It is centered around the Motorola MC68000 [37], a 16-bit microprocessor with a 24-bit address bus. The DBC68K also contains 24

bits of parallel I/O, two RS-232C serial I/O ports, two programmable timers, and a programmable interrupt controller. Sockets are included for an optional Motorola MMU68451 memory management unit, 4K bytes of RAM, and 32K bytes of ROM. The DBR50 memory board contains up to 512K bytes of dynamic RAM, organized as 16-bit words. It includes refresh circuitry and parity generation and check.

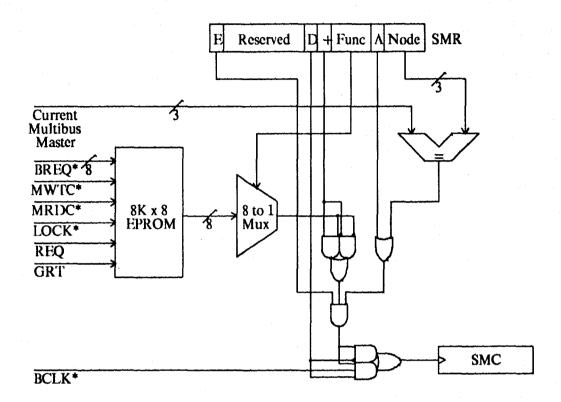

Figure 8: Concert Node - DBC68K Board

Both boards provide two buses, which serve different purposes in the Concert system. They both provide a full IEEE 796 bus [40], a standard bus closely related to Intel's Multibus [9]. The card cage which houses the nodes has a Multibus backplane, and both the processor and memory boards plug into this cage. Both boards also have an interface for a Microbar custom High Speed Bus. Each processor board in a

Concert system uses its High Speed Bus exclusively to access its node memory board. The Multibus backplane allows access to global memory, as described in the next section. Both the Multibus and High Speed Bus interfaces on the processor board are "one-way;" the resources on the DBC68K are not available from off the board.

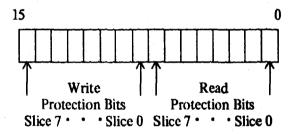

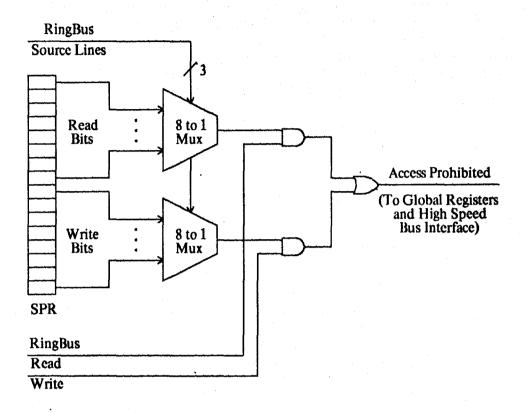

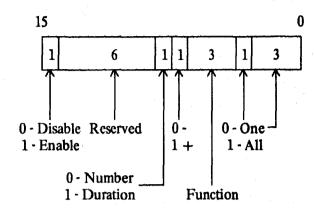

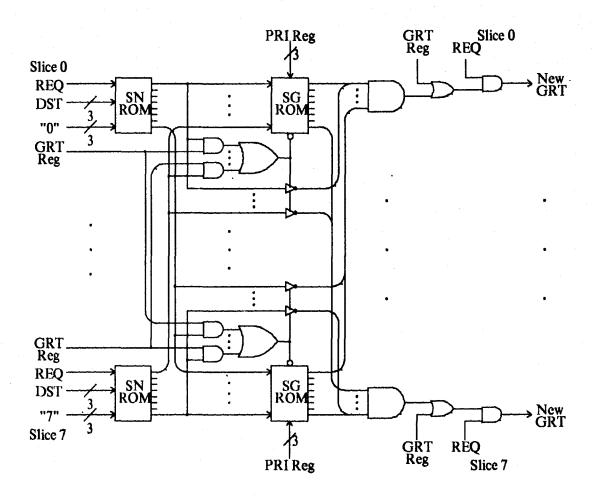

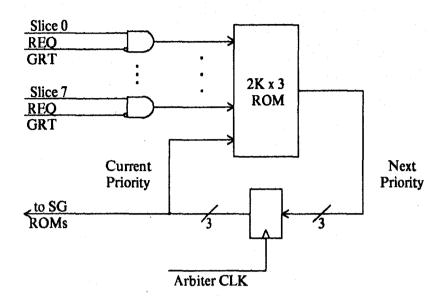

The basic Concert node consists of one DBC68K board and one DBR50 card, and the remainder of the thesis assumes this configuration. However, a number of variations are possible. Multiple memory cards may be connected along the High Speed Bus of a single processor. Other processor boards, such as the Intel iSBC 86/12A [33], can be used instead of the Microbar DBC68K. In fact, any processor with a Multibus interface to plug into the backplane can be used as a Concert node. Some future applications will use floating-point processors or other special nodes to perform specific functions.