### **REPORT -- LEAN 95-01**

#### Toward Lean Hardware/Software System Development: Evaluation of Selected Complex Electronic System Development Methodologies

Prepared by:

Alexander C. Hou

Lean Aircraft Initiative Center for Technology, Policy, and Industrial Development Massachusetts Institute of Technology 77 Massachusetts Avenue Cambridge, MA 02139

February 1995

The author acknowledges the financial support for this research made available by the Lean Aircraft Initiative at MIT sponsored jointly by the US Air Force and a group of aerospace companies. All facts, statements, opinions, and conclusions expressed herein are solely those of the author and do not in any way reflect those of the Lean Aircraft Initiative, the US Air Force, the sponsoring companies (individually or as a group), or MIT. The latter are absolved from any remaining errors or shortcomings for which the author takes full responsibility.

© 1995 Massachusetts Institute of Technology All rights reserved

# TABLE OF CONTENTS

| List of Figures | 3                                                    | ii  |

|-----------------|------------------------------------------------------|-----|

| List of Tables  |                                                      | iii |

| 1               |                                                      |     |

| INTRODUCTIO     | )N                                                   | 1   |

| 1.1             | Overview                                             | . 1 |

| 1.2             | Outline of Report                                    | . 3 |

| 1.3             | The New Calculus                                     | 4   |

| 1.4             | Importance of Hardware and Software                  | . 4 |

| 1.5             | Defining the Development Challenge                   | . 8 |

| 2               |                                                      |     |

| NEW METHO       | DS FOR COMPLEX ELECTRONIC SYSTEM DEVELOPMENT         | 11  |

| 2.1             | Rapid Development DC-X Style                         | 13  |

| 2.2             | Rapid Development the GritTech Way                   | 19  |

| 2.3             | Hardware/Software Codesign                           | 27  |

| 2.4             | Cleanroom Software Engineering                       | 41  |

| 3               |                                                      |     |

| EVALUATING      | THE NEW METHODS                                      | 55  |

| 3.1             | The Criteria                                         | 55  |

| 3.2             | The Rating Scheme                                    | 63  |

| 3.3             | The Evaluations                                      | 63  |

| 3.4             | Conclusions                                          | 71  |

| 4               |                                                      |     |

| CONCLUSION      | S AND RECOMMENDATIONS                                | 73  |

| 4.1             | Tackling the Hardware/Software Development Challenge | 73  |

| 4.2 | Benefits of Lean Hardware/Software Development | 75 |

|-----|------------------------------------------------|----|

| 4.3 | Conclusions and Recommendations                | 77 |

| 4.4 | Recommendations for Further Study              | 79 |

#### APPENDIX

| CLEANROOM ENGINEERING SUPPLEMENT | 85 |

|----------------------------------|----|

| BIBLIOGRAPHY                     | 95 |

## LIST OF FIGURES

| Figure 1.1: Shipments of U.S. Military Aircraft (1980-1994)              | . ? |

|--------------------------------------------------------------------------|-----|

| Figure 1.2: Electronic Content Variation for Selected Systems, 1990-2001 | 5   |

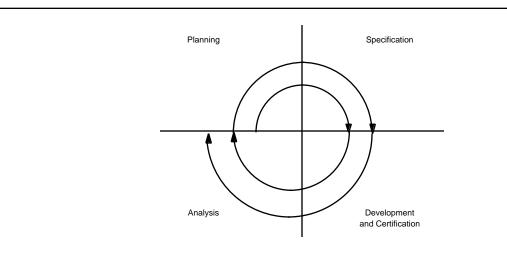

| Figure 2.1: RAPIDS Spiral Development Process                            | 16  |

| Figure 2.2: Integrated Development Environment                           | 24  |

| Figure 2.3: Incremental Development                                      | 26  |

| Figure 2.4: Generic Hardware/Software Codesign Process                   | 30  |

| Figure 2.5: Model Year Design vs. Point Design                           | 36  |

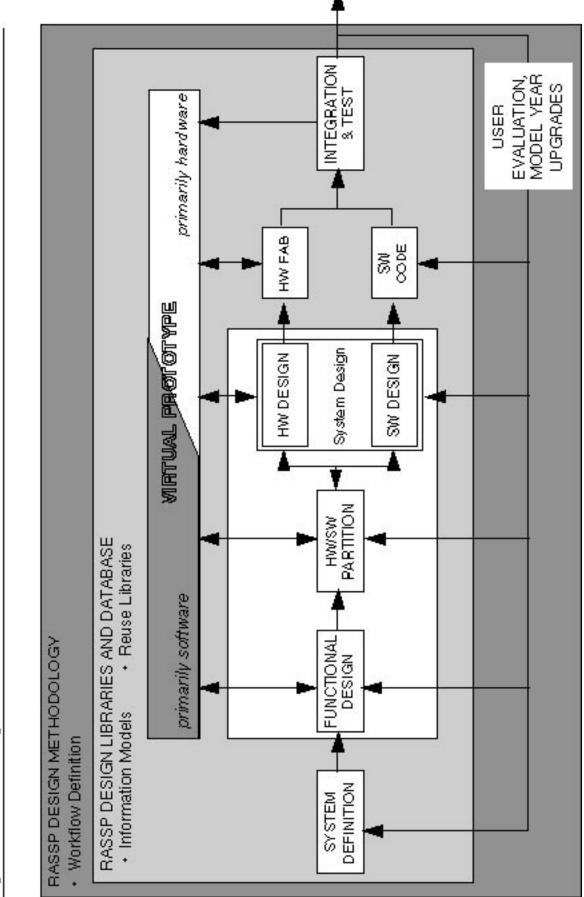

| Figure 2.6: RASSP Design Flow                                            | 39  |

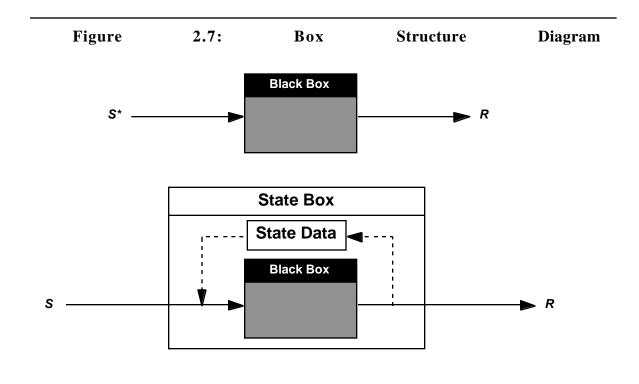

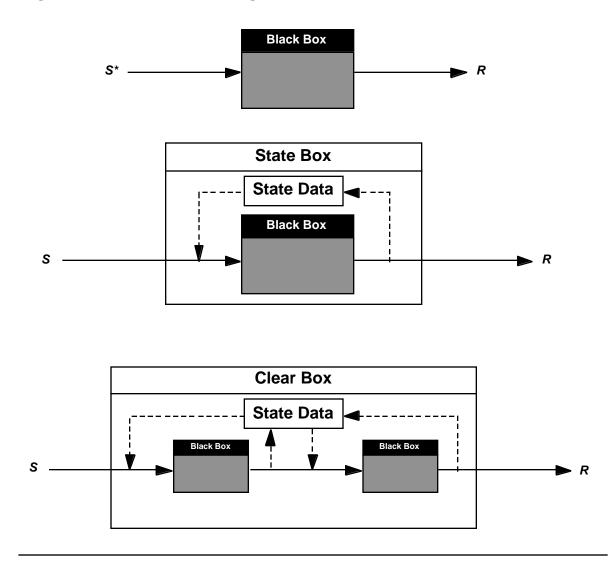

| Figure 2.7: Box Structure Diagrams                                       | 48  |

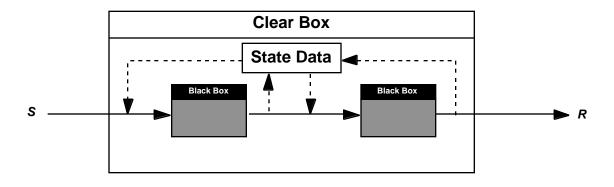

| Figure 2.8: Cleanroom Engineering Spiral Development Process             | 51  |

## LIST OF TABLES

| Table 2.1: | Soyuz Simulation Project Metrics                    | 18 |

|------------|-----------------------------------------------------|----|

| Table 2.2: | Software Rapid Development Results                  | 27 |

| Table 2.3: | Hardware Rapid Development Results                  | 27 |

| Table 2.4: | A Comparison of Software Development Practices      | 44 |

| Table 2.5: | Sample of Cleanroom Results                         | 53 |

| Table 3.1: | Ideal Cross-System Integration Methodology Criteria | 56 |

| Table 3.2: | Process Criteria Matrix                             | 64 |

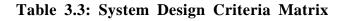

| Table 3.3: | System Design Criteria Matrix                       | 65 |

# CHAPTER 1

# Introduction

#### 1.1 Overview

Since the first flight of a heavier-than-air aircraft at Kitty Hawk on December 17, 1903, aircraft designers have achieved tremendous performance gains in speed, altitude, payload, and range. While these improvements are impressive, evaluating the progress of aeronautics merely in terms of these performance measures would not provide an adequate description of the technology's evolution. In recent years, revolutionary developments in digital electronics and communications have altered basic concepts in military aircraft design and operation. For instance, in the past, with only mechanical flight controls at their disposal, engineers had no choice but to design inherently stable aircraft. Today, digital flyby-wire control systems make possible the design of highly agile aircraft which are unstable—and would otherwise be uncontrollable by a pilot. The impact of information technologies on weapons systems is even more pronounced. Early air combat involved pilots from opposing sides shooting at each other with infantry arms they had carried in their cockpits. Today, engagements can take place beyond visual range and bombs can follow laser beams to their targets.

The advent of information technologies has enabled the Department of Defense (DoD) of the United States to acquire systems with capabilities far beyond what had been state-of-the-art just a few years earlier or had not even existed. Between 30 and 40 percent

of the development and procurement costs of a new weapon system can be attributed to electronic hardware and software. As systems get "smarter", this percentage will only increase. With the declining level of defense expenditures driving industry to adopt lean production practices, the development process for hardware/software systems must be a focal point of efforts to get more "bang for the buck".

The goal of lean development of hardware/software systems poses complex development and acquisition challenges for DoD and American industry. Currently, the development of hardware and software in the defense industry is complicated by the following factors:<sup>1</sup>

- "Material needs" can be satisfied by many combinations of mechanical and electronic systems (hardware and software).

- Technology development processes are heavily influenced by the DoD acquisition process.

- This DoD acquisition process, which evolved to procure mechanical systems, is mechanically-oriented and frequently has difficulty when developing information-based weapons systems.

- Traditional methods partition an electronic system into hardware and software elements and develop these elements separately, despite the tight coupling between "hardware" and "software" in most complex electronic system design problems.

- The administratively driven development process of defense electronic systems is often slower than the evolution of basic electronic technologies, which means that the final program result may be more costly than similar commercially available systems.

<sup>&</sup>lt;sup>1</sup>These factors were identified in the course of field research conducted by Martin Anderson and Alex Hou in support of the Lean Aircraft Initiative consisting of numerous interviews with both government and industry officials. The interview sample included officials from both sponsoring and non-sponsoring companies and government agencies.

As part of the Lean Aircraft Initiative, a research program studying the applicability of lean production principles to the defense aircraft industry sponsored by the Air Force

and over 20 aerospace companies, this report evaluates a set of five complex electronic system development methodologies for applicability as a lean electronic hardware/software system development methodology and analyzes the implications of the evaluation results.<sup>2</sup>

#### **1.2 Outline of Report**

This report is based upon a combination of extensive literature review, including the most contemporary public documents from the Department of Defense, and upon field and phone interviews conducted under the auspices of the Lean Aircraft Initiative.

The remaining sections of this chapter discuss the challenge of reconciling the strategic needs of the American military with the declining level of defense expenditures in the post-Cold War world, the increasing importance of electronics and software in military systems, and the development challenges that have arisen as a result.

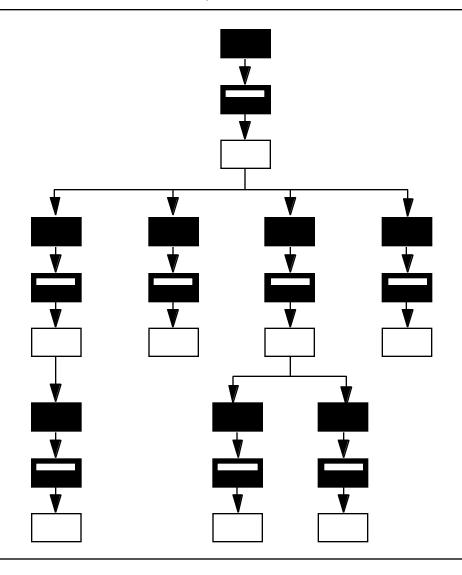

A set of new methodologies for complex electronic system development is discussed in Chapter 2. Each of these methodologies has demonstrated significant improvements in development performance or shows potential for similarly significant improvements.

Chapter 3 describes the criteria that were developed to evaluate the methodologies for possible application as a cross-system integration methodology. Each methodology is evaluated, and the results are discussed. Details of each individual evaluation are also included.

Chapter 4 discusses the implications of the evaluation results. A possible foundation for a lean hardware/software development methodology is described. Conclusions and recommendations derived from this research are summarized. The final section details recommendations for further study.

A more detailed technical description of the practices behind one of the complex electronic system development methodologies evaluated in this report is provided in the Appendix.

<sup>&</sup>lt;sup>2</sup> This report was derived from research performed in the development of a master's thesis written by this author.

#### **1.3 THE NEW CALCULUS**

The end of the Cold War injected a high degree of uncertainty into the national security planning process of the United States. For decades, the subject of how to defeat the numerically superior forces of the Soviet Union and its Warsaw Pact allies in wartime had been the focus of defense planners, strategists, and wargamers in the U.S. and the other North Atlantic Treaty Organization (NATO) countries. Suddenly, our sworn enemies had become our new friends, triggering euphoria over the promise of a new world order and a peace dividend. The depolarization of the world left defense planners without a clear threat to replace the Soviet Union.

However, while the collapse of the Soviet Union has fundamentally altered U.S. strategy and force planning, the need for powerful and decisive U.S. military capabilities endures. If the United States is to remain engaged in world affairs, the ability to bring military power to bear when appropriate to protect its interests, as well as those of its allies, must be maintained. Although there are a wide range of potential military threats to American interests, regional conflicts have become the new focus of U.S. military planning. These types of conflicts present several challenges for the U.S. military including numerous potential locales, smaller forward deployments, short warning times distant deployments, and increasingly capable weapons in the hands of adversaries.

As a part of the reexamination of U.S. national military strategy, the Joint Chiefs of Staff (JCS) recommended that the United States should field forces capable of defeating aggressors in two concurrent, geographically separated major regional conflicts (MRCs).<sup>3</sup> Recently, an evaluation of the capability of U.S. forces to achieve key operational objectives in future major regional conflicts was published by RAND. This study, called *The New Calculus: Analyzing Airpower's Changing Role in Joint Theater Campaigns,* took the two-MRC requirement as a given element of national military strategy and assessed U.S. military capabilities to fulfill the mission—focusing particularly on possible means of enhancing airpower's capabilities in joint operations.

<sup>&</sup>lt;sup>3</sup> In this context, concurrent major regional conflicts are conflicts that erupt sequentially but overlap so that they must be prosecuted simultaneously at times.

RAND's analysis concluded that the projected capabilities of U.S. forces would enable it to satisfy the two-MRC requirement, although the effectiveness of forces in the second theater would be highly dependent on the degree of concurrency of the two conflicts as well as the outcome of the first MRC. Regarding the role of *airpower*, it concluded that *"the calculus has changed and airpower's ability to contribute to the joint battle has increased"* (Bowie et al., 1993, p. 83). The combination of modern airpower's lethality in conventional operations, which has been greatly enhanced by the employment of advanced precision-guided munitions and modern C4I (Communications, Command, Control, Computers and Intelligence) systems, and its strategic mobility and survivability make it a good match for the needs of short-warning MRCs.

To fully exploit the potential of airpower, the RAND study made a number of recommendations aimed at ensuring that U.S. forces could establish and maintain air superiority and enhance its ability to contribute to other aspects of the joint battle. Detailed simulations indicated that equipping current fighters with AMRAAM (Advanced Medium Range Air-to-Air Missile) would ensure air superiority until some time around the year 2000. However, to ensure air superiority over the long term, simulations indicated that a next generation platform, such as the F-22, would be needed in addition to the continued development and procurement of advanced air-to-air missiles (Bowie et al., 1993).

The recommendation to equip our future air forces with more advanced munitions extended beyond the air superiority role to the strategic air offensive and ground campaigns as well. To supplement existing U.S. capabilities—based mainly on fighters and sea-launched cruise missiles—in strategic air offensive operations, the study advocated equipping long-range bombers with precision-guided munitions and standoff weapons, significantly increasing both the effectiveness of early attacks on strategic assets and the rate of destruction of these targets. To enhance the ability of U.S. forces to halt the advance of enemy ground forces and establish an assured defense, RAND's analysis indicated that employment of dispensers equipped with smart anti-armor submunitions, such as the Sensor Fuzed Weapon (SFW), could stop a force of 10 armored and mechanized divisions in approximately half the time required by the same forces armed with current weapons. Furthermore, B-2 bombers equipped with inertially-guided dispensers filled with smart submunitions could be used to provide additional anti-armor capability in the early stages of the conflict and further decrease the time required to halt an armored invasion (Bowie et al., 1993).

The analysis also indicated a need to procure additional fighters such as the F-15E, whose long range, heavy payload, and modern avionics make it a highly effective and versatile asset. Finally, a rapidly deployable theater C4I system—a goal believed to be achievable through the integration of current systems provided that planned upgrades materialize—was deemed essential to the effective and efficient prosecution of airpower's missions within the joint operations framework (Bowie et al., 1993).

Although equipping our forces with advanced munitions, advanced fighters, and rapidly deployable theater C4I systems would allow a smaller force structure to support U.S. national military strategy, these enhancements would surely require a considerable investment. Appropriating funds for this purpose could be difficult since changes in the international security and economic environments have created momentum for the downsizing of the U.S. military and decreasing levels of defense expenditures. This is perhaps the real "new calculus"—cost is now as important as system performance. With the major budgetary impact being felt in procurement which is estimated to be down 47 percent from the peak years of the buildup during the 1980's, the greatest challenge for DoD in the post-Cold War era may be how to maximize its "bang for the buck".

If achieving greater efficiency has become an imperative for DoD, it has become a matter of survival in the aerospace industry. Aerospace industry shipments in 1993 fell 11 percent in real terms and were also expected to fall 11 percent in 1994 from 1993 levels (DoC, 1994). Historically, the industry earned at least half of its revenues from military sales. The worldwide decline in defense spending has reduced the demand for military aircraft, missiles, avionics, and other related equipment from U.S. suppliers. The most recent DoD budget request represented a cumulative real decline in defense spending of more than 40 percent since the peak of the buildup in 1985 (DoC, 1994).

Unlike past downturns in defense spending, the commercial sector has experienced a concurrent slump in demand for its products and is unable to sustain the industry's current level of capacity. Adding to the overcapacity problem are aircraft manufacturers from the former Soviet Union—currently operating at production rates less than one-third of capacity—who have joined the fray in vying for military aircraft sales in the export market (DoC, 1994).

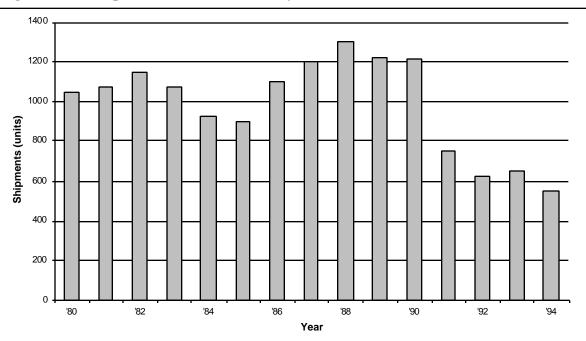

While the aerospace industry in general has suffered greatly during the recent downturn, the military aircraft sector, where the U.S. Government historically accounts for 80 percent of all sales with Foreign Military Sales and direct exports collectively accounting for the remaining 20 percent, has been particularly hard hit by declining defense procurements (DoC, 1994). The resulting downward trend in total shipments of complete U.S. military aircraft is shown in Figure 1.1. While intensifying competition for shrinking defense procurement dollars has driven some companies to diversify into commercial markets or sell off their defense businesses entirely, many have decided to remain focused on the defense market and outlast the competition. For these companies, improving the efficiency and the effectiveness of their operations through the reengineering of business processes and implementation of leaner practices is paramount.

Figure 1.1: Shipments of U.S. Military Aircraft (1980-1994)

Estimates and forecasts for years 1993 and 1994 by International Trade Administration. *Source:* U.S. Department of Commerce, *U.S. Industrial Outlook 1994*.

#### **1.4** Importance of Hardware and Software

Electronic hardware and software are important elements in all the key factors for dramatically increasing U.S. capabilities for destroying enemy forces cited in *The New Calculus:* advanced munitions, avionics, and aircraft and enhanced and rapidly deployable theater C4I capabilities, such as those provided by AWACS and JSTARS (Bowie et al., 1993).

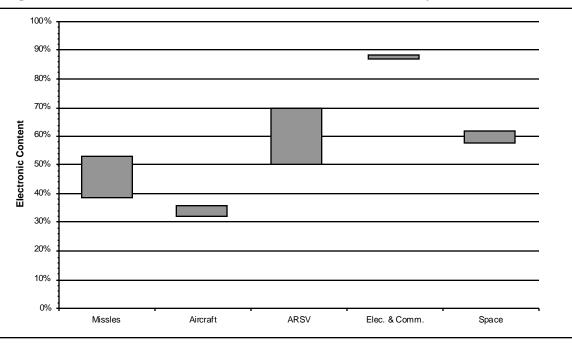

Another indicator of the importance of electronic hardware and software is the high electronic content of military systems. A chart illustrating the forecasted range of variation of electronic content for some typical defense systems is shown in Figure 1.2. Here, electronic content is the percentage of defense procurement and RDT&E (Research, Development, Test and Evaluation) outlays that are devoted to electronics hardware and software. Clearly, the data in Figure 1.2 indicate that all of the selected systems possess a substantial level of electronic content. Even aircraft, which have the lowest level of electronic content of the set of selected systems, are expected to have levels of electronic content ranging between 30 and 35 percent. In modern aircraft development programs, avionics can be the "killer" expense, costing around \$7000 per pound to develop (Rich and Janos, 1994). Missiles contain a higher level of electronic content, and the theater C4I systems—ARSV (Airborne Reconnaissance, Surveillance & Verification) systems, electronics and communications systems, and space systems<sup>4</sup>—possess the highest electronic content levels of all. Overall, the substantial levels of electronic content indicate that electronic hardware and software are integral elements of our military capabilities.

Perhaps the most convincing indicators of the importance of hardware and software are the enhanced military capabilities that are made possible by electronic systems.<sup>5</sup> To fully appreciate the significance of these capabilities, it is useful to consider the past. During World War II, it required 4,500 sorties by B-17 bombers and 9,000 bombs to accomplish what a F-117A can do on one sortie with a single bomb (Toffler and Toffler, 1993).

<sup>&</sup>lt;sup>4</sup> Space systems include C4I assets such as early warning satellites and communications satellites.

<sup>&</sup>lt;sup>5</sup> In fact, many believe that the widespread use and proliferation of advanced information and communication technologies is driving a revolution in warfare (Toffler and Toffler, 1993; Krepinevich, 1994; Arquilla and Ronfeldt, 1992; Hou, 1994).

Figure 1.2: Electronic Content Variation for Selected Systems, 1990-2001

Electronic content was calculated as percentage of procurement and RDT&E outlays devoted to software and electronic hardware. Forecasts for the years 1992-2001 by Electronic Industries Association. Source: EIA (1991)

During the Vietnam War, accomplishing the same mission required 95 sorties and 190 bombs (Toffler and Toffler, 1993). While attempting to destroy the Thanh Hoa bridge, American pilots flew 800 sorties and lost ten planes without achieving success. The bridge stood intact until a flight of four F-4s armed with some of the earliest smart bombs accomplished the task in a single pass (Toffler and Toffler, 1993).

Whereas the crew of a Vietnam-era M-60 tank had to find cover and come to a stop before firing, the crew of a modern M-1 Abrams tank can fire while on the move (Toffler and Toffler, 1993). Similarly, while the chances of a M-60's crew being able to hit a target 2,000 yards away at night are slim, night-vision devices, laser ranging systems, and computerized targeting systems which compensate for heat, wind, and other conditions assure that the M-1 crew will score hits nine times out of ten (Toffler and Toffler, 1993). Clearly, the armored groups whose tanks are equipped with these enabling systems have a significant edge over forces that are not. As was the case with the early smart bombs, the Vietnam War also demonstrated the utility of advanced avionics. Before the fielding of advanced bombing systems, pilots could not do much "jinking" (erratic flight) and still have any chance of delivering their payload on target. The advanced bombing systems compensated for altitude, speed, and a moderate amount of jinking, affording the pilot a significantly higher degree of protection while enhancing his accuracy (Momyer, 1978). Modern systems can enable a pilot to use dumb bombs with a high degree of accuracy.

During the war in the Gulf, precise position information provided by Global Positioning System (GPS) receivers to coalition forces allowed the desert sands to be navigated with a high degree of confidence (Schwarzkopf, 1992). This capability was crucial since the desert was devoid of landmarks—even the sand dunes shifted. The capability enhancing potential of GPS was clearly demonstrated in the first strike of the war by the successful helicopter raid on the Iraqi early-warning radar sites. According to the Pentagon's final report on the Gulf War, the raid was made possible because of night- and low-light vision technologies and the precise navigational capability afforded by the Global Positioning System (DoD, 1992).

While the media made the public aware of the capabilities of precision-guided weapons and other enabling technologies such as night-vision goggles and GPS receivers during the Gulf War, two of the most powerful information weapons of all—AWACS and JSTARS—were relegated to relative obscurity. The E-3 Sentry, otherwise known as AWACS (Airborne Warning and Control System), is a modified Boeing 707 aircraft, crammed with computers, radar, communications gear, and sensors. In both Desert Shield and Desert Storm, the AWACS aircraft scanned the skies in all directions to detect enemy aircraft or missiles, sending targeting data to ground units and interceptors.

The ground-scanning counterpart of AWACS was the Joint Surveillance Target and Attack Radar System (JSTARS). The E-8A JSTARS aircraft is a modified Boeing 707 equipped with a multi-mode radar for detection and tracking of enemy forces, processing equipment, mission crew work stations, and command and control interfaces. Data collected on board are then relayed to six ground station modules that receive radar data processed by the aircraft in real time. The data can then be analyzed by ground commanders for battlefield application (Swalm, 1992).

At the start of the Gulf crisis, the JSTARS system was still in development testing and at least three years remained before an initial production decision was to be made. However, its potential for locating Iraqi tanks was so impressive that the only two existing prototypes were deployed to Saudi Arabia (Swalm, 1992).

JSTARS was initially limited in operations to performing a surveillance role. After only two days, this limitation was removed and a weapons allocation officer was assigned to control his own F-15Es, especially in the campaign against tactical ballistic missile sites. Over the course of operations, Joint STARS evolved to serve in a C4I (Command, Control, Communications, Computers and Intelligence) capacity as part of an interconnected network of these assets, which included AWACS, the RC-135 Rivet Joint electronic eavesdropping aircraft, the Airborne Command and Control Center (ABCCC), and various Army and Air Force command and intelligence centers. Linking JSTARS and AWACS together provided coalition commanders with a comprehensive picture of enemy tactical movements on the ground and in the air (Swalm, 1992).

By all accounts, JSTARS was a boon for coalition forces.<sup>6</sup> Ground commanders could track the movements of enemy forces on a real-time basis, from as far away as 155 miles, under all weather conditions. Aircraft directed by Joint STARS had a 90 percent success rate in finding targets on the first pass, and close air support and interdiction aircraft consistently ran out of ammunition before they ran low on fuel once JSTARS became operational (Swalm, 1992). By the end of the war, the two JSTARS aircraft had flown 49 sorties, logging 535 hours of flight time, successfully detected over 1,000 targets, and controlled 750 fighters. Attesting to the system's revolutionary capabilities, Air Force Chief of Staff General McPeak said, "We will never again want to fight a war without a Joint STARS kind of system."

<sup>&</sup>lt;sup>6</sup> For interdiction missions, JSTARS could use its synthetic aperture radar to provide real-time damage assessment and direct immediate re-attacks. On one occasion, two A-10s and an AC-130 directed by JSTARS destroyed 58 out of 61 vehicles in convoy (Swalm, 1992). In another instance, an Iraqi unit mustering to attack VII Corps was 80 percent disabled before it could engage any of the corps's units (Swalm, 1992). In a similar scenario, a unit of the Republican Guard preparing to launch a counterattack was detected by JSTARS and targeted from a ground station and destroyed by Army Apache attack helicopters (Swalm, 1992). JSTARS also played a significant role in hunting mobile Scud launchers, first locating their positions and then passing that information on to ground-based and airborne strike assets (Swalm, 1992).

#### **1.5 DEFINING THE DEVELOPMENT CHALLENGE**

While electronic hardware/software systems are integral to the performance of defense systems, the development of hardware and software in an effective and efficient manner remains an elusive goal. High quality and reliability are extremely important since even small errors can severely degrade the performance of the system.

For instance, the AMRAAM program experienced both the difficulties involved in integrating AMRAAM software with various aircraft systems and the adverse effects of minor software problems. In one four-on-four test, all four missiles failed to hit their targets. Three missiles failed because the radar detected false targets. The failure of the fourth missile was caused by a software problem—a constant that the missile's computer used in some calculations was wrong—that required only a few lines of code to be changed (Mayer, 1993).

In addition to the challenge of developing and fielding high-quality hardware and software, it is also necessary to consider other factors that should shape the development challenge. The following is a list of some of these factors:

- *a) Declining defense outlays.* Cuts in the defense budget will result in lower levels of development and procurement expenditures.

- b) Long service lives. Historically, defense systems tend to have longer service lives than were originally intended at the outset of development. In addition, since DoD will not be able to afford as many new systems as it has in the past, fielded systems and newly developed systems may have their service lives stretched out even longer than in the past.

- c) Rapid improvement of technology. Modern weapons systems have a high degree of electronic content. The performance of electronic hardware and software technologies continues to advance rapidly and shows no signs of slowing down. The performance of these technologies that are such an integral part of theater systems can improve dramatically over the service lifetime of a fielded system.

*d) Growth in complexity.* Demands for ever more advanced capabilities and the rapid improvement of technology have created a rapid increase in the complexity of new electronic hardware/software systems.

Factor **a** highlights the importance of ensuring the development of electronic hardware/software systems in an affordable manner. Factors **b** and **c** point to the need for newly developed electronic hardware/software systems to be upgradable, evolvable, and maintainable. Factor **d** points to the need for a development methodology which can be scaled to cope effectively with the increasing complexity of advanced electronic systems.

Thus, a lean hardware/software system development methodology must be scalable and be capable of producing a high-quality product that is affordable, upgradable, evolvable, and maintainable.

# **New Methods for Complex Electronic System Development**

To effectively address the challenges of developing modern complex electronic hardware/software systems, a lean development methodology needs to be devised. With this in mind, a set of complex electronic system development methodologies was investigated with the hope of finding a methodology that could be directly applied in this role or could at least provide a starting point for the development of a suitable methodology. This set included the following methodologies:

- The rapid development process used to develop the flight control software for the DC-X

- The GritTech rapid development process

- Ptolemy-supported hardware/software codesign

- The RASSP (Rapid Prototyping of Application Specific Signal Processors) design methodology<sup>1</sup>

- Cleanroom software engineering

Each of the methodologies described in this chapter has produced significant improvements in the development of complex electronic systems or shows great potential

<sup>&</sup>lt;sup>1</sup> Note that both Ptolemy-supported hardware/software codesign and the RASSP design metodology are grouped together loosely under section 3.3, "Hardware/Software Codesign."

for producing similarly significant improvements. These methodologies will be evaluated in Chapter 3 for their applicability as a lean hardware/software development methodology.

"Complex electronic system" is an umbrella term used to denote any system or group of systems which contain a large amount of electronic<sup>2</sup> hardware and software. Complex electronic systems can range from RAM-based field programmable gate arrays or digital signal processors running assembly code algorithms to JSTARS and beyond to include what we have denoted as "theater systems".

These systems are inherently "complex" because of the dramatic increase in the complexity of the hardware and software that are used in the development of even "simple" products. Consider, for instance, the development of a printed circuit module. The number of semiconductor gate equivalents contained by a typical (6 inch x 9 inch) printed circuit module increased by a factor of 20 between the 1980s and the 1990s. In the 1980s one of these modules ran at clock speeds between one and five megahertz. In the 1990s a module of similar size might run at clock speeds of 50 MHz or more. The size and complexity of the software contained in the modules has also displayed a similarly explosive rate of growth. Today, one of these modules may store more than four megabytes of code and/or data.

This growth in complexity is also evident at the avionic system level. The F-4s that saw combat in Vietnam did not have a digital computer on board and had no software. The first fighter aircraft equipped with digital computers were developed in the 1960s. These systems, which performed fire control tasks, required between 100 and 200 four- to eight-bit words of assembly language code. In the 1980s the software requirement had grown to approximately 400,000 eight- to sixteen-bit words of a combination of assembly language and higher-order languages to perform more complex functions including fire control, navigation, engine control, built-in-test, electronic warfare, flight control, stores management, and controls and displays (EIA, 1988).

This shift from solving relatively simple problems in software to solving problems of much greater complexity occurred during the mid 1970s. The F-16As, developed during the 1970s, were equipped with seven computer systems, 50 digital processors, and

<sup>&</sup>lt;sup>2</sup> For the purposes of this report, other types of systems, such as photonic or optoelectronic, could also fall under the broad category of "electronic systems."

135,000 lines of code (EIA, 1988). Produced in the late 1980s and early 1990s, the F-14D has 15 computer systems, 300 digital processors, and 236,000 lines of code. The B-2 reportedly has over 200 processors and approximately 5 million lines of code (Anderson and Dorfman, 1991). Currently, the F-22 has approximately 1.3 million lines of code on board, and has 4 million lines of code when the fighter's support systems are included.<sup>3</sup> Even transport aircraft exhibit this explosive growth in hardware and software complexity. The C-17, which is the most computerized, software-intensive, transport aircraft ever built, has 56 computerized avionics subsystems which use 19 different types of embedded computers incorporating over 80 microprocessors and nearly 1.36 million lines of code (GAO, 1992).

The explosive growth in the complexity of hardware/software systems has made the development of these systems all the more difficult. The rate of increase in difficulty of system design and integration problems threatened to outstrip the rate of improvement of methods developed within existing paradigms. This realization provided the impetus for the creation of the methodologies discussed at length in the remaining sections of this chapter.

#### 2.1 RAPID DEVELOPMENT DC-X STYLE<sup>4</sup>

For the past several years, McDonnell Douglas Aerospace-West (MDA-W) has been developing a flight software development process known as RAPIDS (Rapid Prototyping and Integrated Design System). McDonnell Douglas Aerospace has applied RAPIDS to more than 15 projects including several flight and ground test programs including Single Stage Rocket Technology (SSRT) and Ground Based Interceptor. Phase II of the SSRT Program, awarded to MDA-W in August 1991, provided another opportunity to demonstrate the effectiveness of this methodology.

As a result of customer insight, software development, cost, schedule and reliability issues were closely scrutinized early in the program. This provided MDA-W with the

<sup>&</sup>lt;sup>3</sup> Telephone interview with Chris Blake, Avionics IPT leader, F-22 SPO. July 16, 1994

<sup>&</sup>lt;sup>4</sup> This section is based upon phone interviews with Mr. Matt Maras of MDA-W and Dr. Jo Uhde-Lacovara of JSC's Rapid Development Laboratory and publications which they provided (Maras et al., 1994; Uhde-Lacovara et al., 1994).

opportunity to propose the use of a non-traditional process based on an integrated system level approach to the Guidance, Navigation, and Control (GN&C) design.

The entire Operational Flight Program (OFP) used by the Delta Clipper Experimental (DC-X1) was designed, coded, integrated, and tested in 24 months. The 66,000 source lines of Ada code were used by the DC-X1 to complete nine system level static fire tests and three fully successful flight tests. Encompassing an autonomous GN&C capability, the flight control portion of the OFP was developed entirely within the integrated design and rapid prototyping environment.

In addition to the flight software (FSW) developed with this approach, test code, representing high fidelity models of the vehicle, its aerodynamics, sensors and actuators, and winds were also designed by employing the same methodology. Almost 70 percent of the new vehicle software developed for the DC-X1 program was produced with the integrated design environment, using automated code generation (Maras et al., 1994).

#### 2.1.1 The Traditional Approach

The traditional approach to developing flight software displays the symptoms of what Hammer and Champy (1993) refer to as "process fragmentation". Engineers skilled in particular problem domains formulate detailed requirements for the systems and subsystems. During the requirements design phase, engineers develop and test candidate GN&C algorithms. A non-real-time engineering simulation is created to compare the performance of different algorithms. Several reviews are scheduled during this phase resulting in the elimination of some algorithms from further consideration. Following the selection of an algorithm or a set of algorithms, a requirements document is written.

These requirements are then passed on to other organizations which interpret the requirements and translate them into actual computer code. Once the code is written and tested, it is delivered to organizations responsible for the integration of the hardware with the software and testing of the resulting system. Typically, this is where many unforeseen problems arise—late in the schedule where problems are most difficult and costly to fix. Corrections are especially costly when changes to the requirements must be made. For example, a change in the mission requirements may necessitate changing the flight software requirements. These changes can require extensive modifications to the FSW. To

make matters worse, the change process is usually conducted in the same fragmented, sequential manner as the original design iteration.

#### 2.1.2 The RAPIDS Process

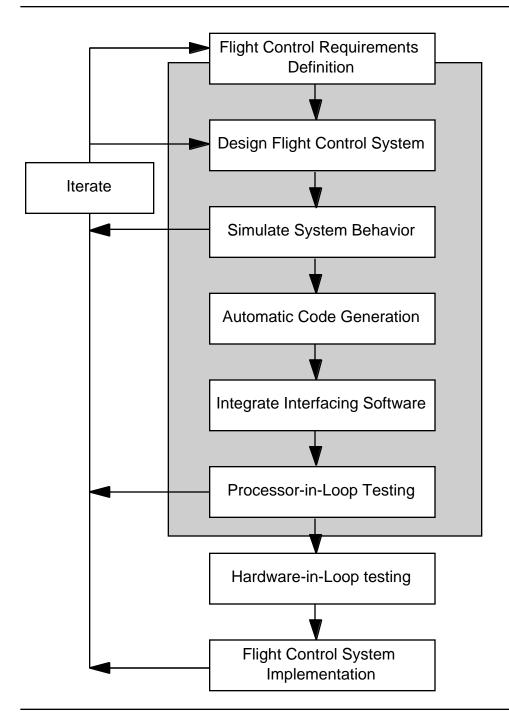

RAPIDS is a highly iterative process utilizing rapid prototyping techniques. Each rapid prototyping cycle develops a complete GN&C system from requirements definition through design and implementation on a target processor. Processor-in-loop (PIL) testing is performed once the initial working FSW prototype is developed.

This approach allows problems with software design, implementation, or hardware selection to be discovered early in the development cycle. This cycle of concurrent requirements and software development and PIL testing is repeated until FSW with the desired performance and quality is produced. The approach employed by RAPIDS is a spiral development approach where developers "build a little, test a little". This process is illustrated in Figure 2.1.

Each RAPIDS design cycle involves phases which can be found in a traditional process—requirements, design, development, and integration and test—that are performed with varying degrees of concurrency. Cycle time decreases with each iteration while the quality of the FSW increases. Whereas a traditional approach may require years to complete a single design cycle, initial iterations of a RAPIDS process may require months and then only weeks as the design matures. Ultimately, the design cycle may be on the order of a few days or less. However, regardless of the length of the design cycle, configuration control and complete software validation testing are maintained.

A designer in a RAPIDS process is part of a small, integrated team and is involved for the whole design, development, and validation process. Using an integrated team of system designers means that the distinctions between systems engineering, GN&C engineering, and software engineering break down—a single team member may be asked to perform any of these functions over the course of a development program. Whereas in the past each functional discipline would own only a portion of the final design and only a certain phase of the program, the RAPIDS design team has ownership of the entire process and end product. Indicators are that end-to-end ownership of the product and process tends to be more efficient and promotes a more productive work environment for the designers (Maras et al., 1994).

Figure 2.1: RAPIDS Spiral Development Process

*Note*: Hardware-in-loop testing involves the actual flight hardware. Processor-in-loop testing is performed with commercially equivalent hardware.

#### 2.1.3 **RAPIDS** Toolset

The RAPIDS toolset integrates requirements analysis through hardware and software testing in a workstation environment using an integrated set of commercial off-the-shelf software development and simulation tools. The graphical user interface toolset captures design details being implemented by GN&C experts and then automatically generates source code and documentation that can be targeted to the actual flight vehicle computer system. The environment is currently based on commercially available products including ISI's (Integrated Systems, Inc.) MATRIX<sub>X</sub>/SystemBuild/AutoCode/AC-100<sup>TM</sup> and Cadre Teamwork.

MATRIX<sub>X</sub>/SystemBuild is a graphical software tool that enables users to develop data flow block diagrams of the desired system using elementary building blocks. These elementary blocks can be organized into "Superblocks" which become procedures or subtasks. This construction process yields highly modular software designs which can facilitate the development of generic software libraries and the reuse of software. After construction is completed, the software data flow diagrams can be interactively tested in a non-real-time environment. Time and frequency domain analyses can also be performed interactively.

The AutoCode tool can automatically translate the block diagram representations into FORTRAN, C, or Ada source code. The source code can then be integrated with other interfacing software—software necessary for the code to run on the target processor such as a real-time operating system device driver, compiled and run on the AC-100 real-time computer to verify real-time and PIL performance.

#### 2.1.4 Benefits of the RAPIDS Process

The ultimate benefit of this approach is a cost reduction because of the smaller software development staff necessary to support initial requirements definition through test and integration. The reduction in software development staffing is possible since the application or GN&C designer does the majority of these activities within an integrated, graphical workstation environment. Other benefits of the methodology include the following:

- Software is not a schedule critical item, and the best design can be implemented at flight time because it is not limited by the typical six to twelve month lead time required by a traditional process to make software changes. The design that flies can be based on the best available data and algorithms from all previous testing.

- Challenging milestones, which are typical of fast paced programs, can be met while maintaining or enhancing the quality of the final software product.

- The rapid prototyping process allows major errors and design flaws to be discovered earlier in the program when they are cheaper and easier to correct.

- Requirements can be verified early in the development program.

- Metrics tracked during DC-X1 software development indicated that the RAPIDS process can result in productivity improvements greater than 25 percent.

The Navigation, Control & Aeronautics Division at NASA's Johnson Space Center employed a similar process to construct a simulation of the Soyuz Assured Crew Return Vehicle flight software and demonstrated substantial productivity gains when compared to COCOMO model estimates. The data are shown in Table 2.1.

|                                           | Phase 1 | Phase 2            |

|-------------------------------------------|---------|--------------------|

| Number of Superblocks                     | 55      | 371                |

| Number of SLOC                            | 4102    | 25045 <sup>a</sup> |

| COCOMO Estimated Total Staff-Hours        | 3400    | 11658              |

| Estimated Total Staff-Hours               | 1830    | 7720               |

| SLOC per Staff-Day                        | 18      | 22 <sup>b</sup>    |

| Productivity Increase (Actual vs. COCOMO) | 85%     | 50%                |

#### Table 2.1: Soyuz Simulation Project Metrics

Source: Uhde-Lacovara et al. (1994)

a. This figure includes the lines of code produced in Phase 1.

b.Reuse of Phase 1 software is assumed. Thus, the number of SLOC from Phase 1 was not included in calculating this value.

#### 2.2 RAPID DEVELOPMENT THE GRITTECH WAY

Recognizing that the rate of complexity growth in electronic hardware and software was rapidly outdistancing the ability of its engineers to keep pace, GritTech<sup>5</sup> began to experiment with rapid development processes and enabling technologies to determine if dramatic improvements in productivity could be made. The basic question addressed in formulating a rapid development process was how to change the traditional process to exploit more fully the potential of design automation tools.

At GritTech the traditional development process for a typical module involved 30 or more discrete steps which were performed in a sequential, isolated fashion. Experience with this process taught the designers that the traditional process would often lead to the propagation of flaws which would remain undiscovered until late in the development cycle where rework can be a most costly and time consuming process. For instance, a small misinterpretation of the customer's specifications on the part of the contractor early on in the development process could embed a flaw in the design that could escape detection until field tests are conducted at the end of the development chain. Corrective action in this case could very well be a lengthy and expensive process. Even when errors remain undetected for only a few steps in a sequential process, the result could be significant budget and schedule overruns.

GritTech's answer to the productivity problem was to search for development processes which tightly integrated the diverse tasks so that they could be performed in parallel with rapid feedback and feedforward of information among all tasks. They believed that productivity would increase dramatically if the person doing a task could see the impact of a contemplated change on the results of all other tasks within minutes, rather than months.

#### 2.2.1 General Process Characteristics and Philosophy

The rapid development process is composed of several technical and procedural elements. The relative importance of an individual element depends on the type of development

<sup>&</sup>lt;sup>5</sup> This is a pseudonym for a defense electronics firm's rapid development group whose practices were studied for this report. The pseudonym is being used, at the request of the firm, in the interests of preserving confidentiality.

project at hand. Reflecting a kind of "skunk works" approach to project management, the designers responsible for the undertaking are given a wide degree of latitude in tailoring the process to the needs of the current project.

In addition, designers involved in rapid development projects generally have more responsibility for the project than designers working on a more traditionally managed program. For instance, the actual system designers are often personally involved in meetings with the customer. Project managers are also more involved with the day-to-day work of the designers, often getting involved in actual design activities themselves. The combination of broader responsibility for designers and more involvement by project managers facilitates better assessment of the current status and rate of completion of project work.

The rapid development designers are all high caliber engineers. If some "ilities"<sup>6</sup> are not required to satisfy customer requirements and are tailored out of the official project process in order to meet tight scheduling constraints, the individual designers will still try to account for them informally as a part of exercising "good engineering practice". For instance, consider a technology demonstration project under such time pressure that tasks such as explicit design activities, which are meant to ensure a certain degree of expandability, are tailored out of the official project process. However, a project engineer may still include some spare pin locations on a board in order to easily accommodate the addition of more memory or processing power in case it becomes necessary to increase the functionality of the system in the future.

A major tenet of the rapid development operating philosophy is to utilize all available means to enhance productivity and to allow the designers to experiment with new technologies to accomplish this. This tenet manifests itself operationally in a number of ways. For instance, designers in the rapid development group at GritTech utilize the Internet to get advice from outside experts. Frequently, assistance and advice can be obtained for free from the many technically-oriented newsgroups on UseNet. Source code applicable to a project at hand can also be found via ftp (file transfer protocol) or gopher sites. This tenet has also manifested itself in the willingness of designers to experiment

<sup>&</sup>lt;sup>6</sup> "ilities" is shorthand for a class of design considerations such as manufacturability, affordability, supportability, scalability, upgradability, producibility.

with and adopt new design tools. In several instances designers have even adopted new design tools and used them for the first time on actual projects that were already in process, believing that the tools would help them perform their tasks better and faster.<sup>7</sup>

Typical rapid development projects do not attempt to extend the state-of-the-art in electronic hardware and software technologies. Most involve exploiting state-of-the-shelf technologies in new ways to produce a desired capability or set of capabilities. Demanding schedules are part of the norm.

To reduce the risks involved with development projects, the group does not usually attempt projects unless it has had some prior experience with the technologies involved. In some cases the group has even conducted some rapid prototyping activities before submitting a bid to ensure that risks are understood. Sometimes even hardware components will be part of the rapid prototyping effort. To further reduce risks involved in a development project, rapid development engineers will use real data whenever it is available since simulated data can be imperfect.

#### 2.2.2 Examples of Rapid Development

As previously mentioned, GritTech's rapid development process and operating philosophy allow engineers extensive latitude in tailoring the process to the particular needs of the project. Moreover, most of the projects performed by the rapid development group at GritTech do not involve product line systems. Hence, it is useful to briefly examine a couple of rapid development projects—one hardware/software system and one software application—to gain a better understanding of the methodology.

#### Hardware/Software System Development

A good example of the application of GritTech's rapid development philosophy to hardware/software system development involved the design and development of an acoustic processor. The objective was to take a power-hungry, computation intensive system and develop a portable, low-power system providing equivalent functionality. Since

<sup>&</sup>lt;sup>7</sup> Another aspect of this constant search for new tools and methods is the group's resistance to standardization of tools and processes. According to rapid development engineers, the traditional usage of standardization—one in which tools and processes that are standardized remain the company's standard even though much better tools and processes may exist—overly constrains the ability of a designer to use the best available tools and methods.

the chosen low-power processor provided only a fraction of the original system's computational power, it was necessary to decrease the computational load of the algorithms without appreciably degrading the performance of the system. Adding to the challenge was a four month development schedule.

Since simulation models were not available for some components that had been chosen for use, the hardware design needed to be prototyped and verified before the actual printed circuit board was fabricated. While wire wrapping—the traditional prototyping technology—can be relatively inexpensive, it was not flexible enough for the project's demanding schedule. The wrapping of the initial design can take a week, and corrections to the design can be time consuming and are often not properly documented, which can cause significant problems during hardware debugging. Consequently, a new, flexible prototype technology was chosen—Field Programmable Interconnect (FPIC) devices and Field Programmable Circuit Boards (FPCBs).<sup>8</sup>

Utilizing the flexible prototyping technology, the prototype could be dynamically reconfigured based on changes to the schematic—a capability that proved its worth on many occasions. For instance, an easily-acquired SRAM (Static Random Access Memory) was used initially instead of the desired SRAM since the special, low-power SRAM selected for the design was unavailable at the start of hardware development. When the desired components were delivered, the design schematics were updated to account for the different packaging and pin layout, and the new netlist was downloaded to the FPCB within minutes. In the course of development, a bit-swap error was detected which could have forced an entire bus change and a one day delay if wire wrapping had been used. Instead, the FPCB-FPIC combination enabled a corrected design to be up and running within minutes.

The flexibility of the prototype technology allowed the hardware design to be completely debugged in one week without the aid of computer simulations. A conventional

<sup>&</sup>lt;sup>8</sup> The FPIC is a commercially-available RAM-based passive routing device, containing over 900 usable input/output pins. The FPCB is a multilayer circuit board accommodating an array of pin sockets and a mounting area for one or more FPICs. A circuit is constructed by placing components on the board and configuring the FPICs. The FPIC also has a dedicated logic-analyzer diagnostic port. Extensive software tools for translating netlist information into component placement, FPIC internal routing, and logic-analyzer configuration information are also available from the vendor. FPIC and FPCB are trademarks of Aptix Corporation.

printed circuit board layout was performed concurrently with the hardware design verification effort, and schematic changes made as a result of the debugging effort were automatically included in the printed circuit board (PCB) layout. After only one week of testing, the PCB was shipped for fabrication using the identical netlist that had been validated on the prototype. When the bare PCB was delivered, the components were dropped in, and the system was thoroughly tested. After two days of testing, no defects were discovered, and the board was declared finished with no cuts or jumpers required. No problems have been reported in subsequent operational use.

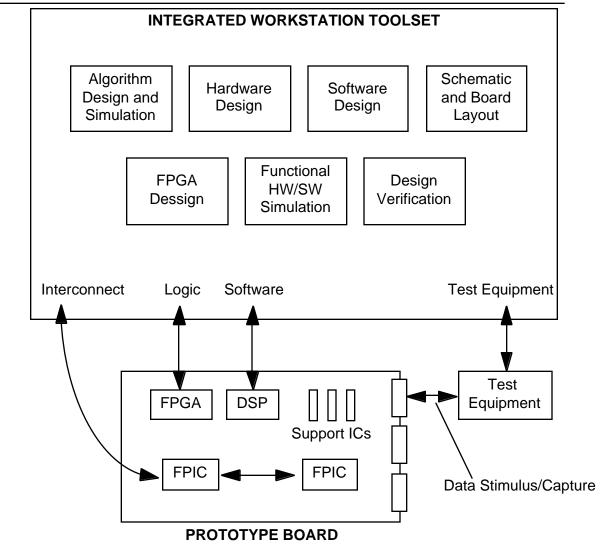

While the PCB was being fabricated, the application software was being coded and tested using the integrated development environment, which included the FPCB-FPIC prototype, an in-system processor emulator, networked logic analysis instruments, a "reference design" from a previous project, and additional signal processing analysis tools running on a workstation. A depiction of this environment is shown in Figure 2.2. The combination of the ability to control the hardware and test equipment from the workstation by downloading and uploading code, data, and sequencing information and the ability to orchestrate the use of the various assets with operating system scripts provided designers with a powerful, integrated rapid development environment. Moreover, having a completed printed circuit board in a little more than one month enabled the designers to focus their efforts on developing more sophisticated algorithms during the remaining three months and achieve better field-test results.

In addition to the speed of development afforded by the integrated environment, application software development was further accelerated through the use of several routines that were obtained from bulletin boards on the Internet. These routines provided the needed throughput with minimal modification.

According to the designers, the success of the rapid development project could be attributed to the use of a combination of newer technologies which resulted in a major reduction in development time. Compared to estimates of traditional development effort based on a benchmark of 15 staff-months/board for typical module development productivity, the hardware/software effort required only 16 percent of the engineering staff-months. Thus, by combining an integrated development environment with

Figure 2.2: Integrated Development Environment

programmable prototype methods, the GritTech rapid development engineers achieved a factor of six improvement in productivity.

#### Incremental Software Development

Another example of rapid development in action was the use of the process in the development of a launch data visualization and advising system. This particular project arose from the customer's desire to exploit newly available data visualization capabilities for a launch vehicle program in 1991. Over 50,000 pressure, temperature, wind direction, and other sensors were in use during launch preparations. The data stream from these

sensors was being preprocessed and displayed to operating personnel in the form of instantaneous numeric values. The customer identified a need to display this information graphically, provide trend information at a glance, enable comparisons to past launches, and perform related functions.

Rapid development engineers developed a core analysis and display system in about a month after project launch. This initial release was then installed for evaluation on computers at the launch facility, off-line from actual launch operations. Incremental release of the most recent version for customer evaluation occurred approximately every five weeks. Feedback included the suggestion to add capability to call up video views of the launch vehicle and the launch pad. The GritTech engineers discovered that the incremental development and release approach also helps to build a good working relationship with the customer in addition to speeding up the development process. Design cycles tend to get progressively shorter with each iteration, partly because the integration of software modules is performed many times and gets progressively easier.

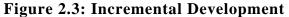

The incremental development process is depicted in Figure 2.3. Incremental development utilizes a series of quick low cost field trials of progressively more complete systems. This approach differs considerably from the traditional approach which defers field testing until the end of a multi-year, full scale development program.

In the incremental development process, software design and development can begin as soon as some part of the system specification has been developed. Typically, the specification or portion of a specification is translated into a field-testable design in about a month. The customer is then supplied with a copy of the current software for operational or test range evaluations of the design with the GritTech designers providing support. This field testing is especially important for evaluating the design of user interfaces and displays. Based on the results of the joint evaluation, the specification is extended or revised, and the design is incrementally expanded and/or refined during the next cycle.

The rapid development group has found from past experiences that the optimum time period for providing customers with opportunities for hands-on evaluation is approximately once every four to ten weeks. The result is a design that rapidly evolves into a well-suited, highly functional system with minimal need to expend resources on

performing rework resulting from erroneous assumptions and interpretations of requirements.

As was the case with the acoustic processor example, using a highly integrated set of software development tools facilitated a substantial reduction in the time and effort required for system development. One tool allowed software engineers to design the graphical user interfaces (GUIs) by manipulating basic GUI building blocks available from a palette. Once the elements were arranged to the satisfaction of the engineer, the actual source code was produced through automatic code generation. As a rule the generated code was not touched unless problems could be explicitly traced to it. Another tool which helped speed development enabled designers to execute the code and see how it worked without having to compile it first. Software libraries also facilitated the reuse of previously developed and verified software modules.

Since the launch data visualization system uses virtually all commercial off-the-shelf workstation and video hardware, development productivity was only measured with respect to the software development benchmark of 10 standard lines of code per staff-day. By using a highly integrated suite of software development tools in conjunction with an incremental development approach, the rapid development team was able to develop this system and demonstrate an 8:1 improvement in productivity in spite of having to absorb a significant revision to the performance requirement.

#### 2.2.3 Rapid Development Productivity Performance

To date, the rapid development process has been used on 20 different small to medium sized projects at GritTech, demonstrating significant productivity improvements over a traditional process in each case. The improvements in productivity afforded by the rapid development methodologies and tools for these projects are summarized in Table 2.2 and Table 2.3 for software and hardware development, respectively. The rapid development projects have consistently exhibited two to four times the productivity that would be expected of a traditional process.

Table 2.2: Software Rapid Development Results

| Environment            | Productivity Improvement<br>(versus benchmark) |

|------------------------|------------------------------------------------|

| Tailored DoD-STD-2167A | 3 to 4:1                                       |

| Other                  | 3 to 8:1                                       |

Table 2.3: Hardware Rapid Development Results

| Module Type                                 | Туре                 | Productivity Improvement<br>(versus benchmark) |

|---------------------------------------------|----------------------|------------------------------------------------|

| 6 inches x 9 inches<br>(54 square inches)   | Microprocessor-Based | 2 to 6:1                                       |

| 8 inches x 16 inches<br>(128 square inches) | Logic-Based          | 2 to 4:1                                       |

#### 2.3 HARDWARE/SOFTWARE CODESIGN

Methodologies to support the codesign of hardware/software systems were developed in response to problems with the traditional process for developing these systems. The traditional process partitioned the problem into hardware and software elements early in the development cycle, and then proceeded to develop the two designs in parallel with very little or no interaction until the end of the process when they were integrated for system

testing. Predictably, the classic approach exhibits many symptoms of a fragmented process.

Typically, the integration of the hardware and software near the end of the development cycle is laden with unforeseen problems—many of which can be attributed to the lack of interaction between the hardware and software design groups. Any design changes at this point in the process are likely to significantly impact the system's cost and development schedule. In many instances, even when integration itself does not reveal any problems, the overall system performance can be disappointing. Frequently, the blame is laid at the feet of the programmers. However, in many cases, the real fault may lie in the design of a development process which imposes an artificially crisp distinction between hardware and software design.

# 2.3.1 Generic Hardware/Software Codesign Process

An alternative approach is to recognize the high degree of coupling that exists between hardware and software for most complex electronic system design problems and employ a more flexible design process, where hardware and software development proceed in parallel with feedback and interaction between the two as the overall system design matures. The final hardware/software partitioning decision can be made after evaluating alternate design architectures with respect to such factors as performance, programmability, reliability, and manufacturability. This type of approach may be termed "hardware/software codesign".

According to Kalavade and Lee (1992), hardware/software codesign strategies can be applied to different levels of design problems including:

- *Processor Design.* An optimized application-specific processor can be developed by tailoring both the instruction set and the program for the application. This type of codesign problem is very difficult.

- *System-Level Design*. Hardware/software codesign can also be performed at the system level, where an algorithm is partitioned between custom hardware and software running on programmable components. The hardware would typically include discrete components, application-specific integrated circuits (ASICs),

DSP cores, microprocessors, microcontrollers, or semi-custom logic developed using FPGAs or logic synthesis tools. Since there are many possible ways to partition a given design between hardware and software components, evaluating design configurations with system-level simulation of hardware and software allows the design space to be more thoroughly explored and is an integral part of codesign.

Application-Specific Multiprocessor System Design. The codesign of an application-specific multiprocessor system is challenging since it involves choosing a suitable number of processors, an interprocessor communication (IPC) strategy, and the design of the application software. Since software synthesis requires partitioning and scheduling the code among the processors, scheduling techniques must be capable of adapting to changing hardware configurations. Thus, developing an application-specific multiprocessor system is an iterative process, involving tradeoffs associated with selecting an optimal hardware configuration and software partitioning.

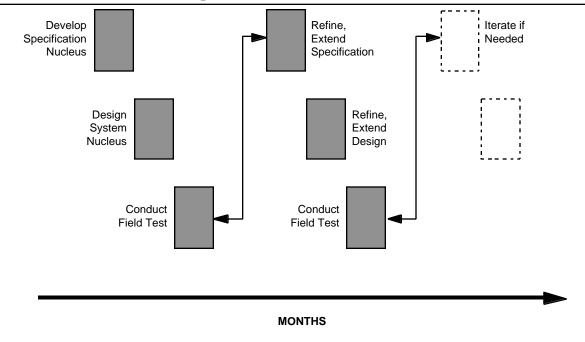

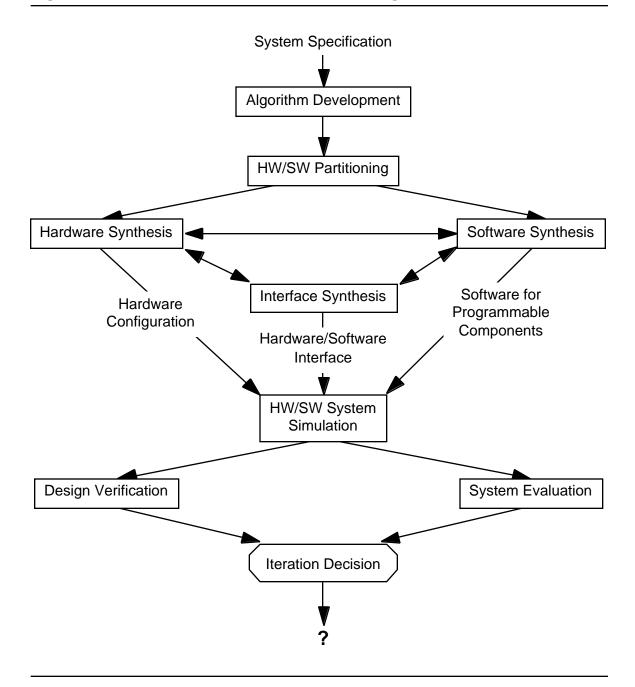

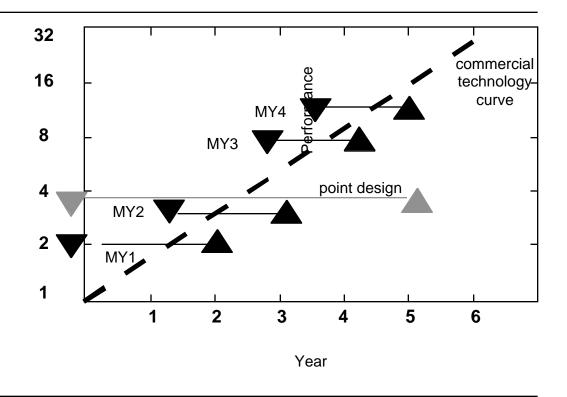

A generic hardware/software codesign process is shown in Figure 2.4. The objective of a codesign methodology is to produce a hardware/software system design that meets a given set of specifications while satisfying a set of design constraints. Given a system specification, a designer can utilize high-level functional simulations to develop a suitable algorithm without making any assumptions concerning specific implementation details. The next step is to partition the algorithm into hardware and software while satisfying requirements such as speed, complexity, and flexibility. Operations that are computationally intensive with fixed operations are usually allocated to hardware. Algorithm components that may vary for different situations, are less computationally intensive, may require field programmability, or are not likely to change with time can be allocated to software (Kalavade and Lee, 1993).

Once the initial partitioning has been performed, the process of synthesizing the hardware, software, and interface designs can begin. These three activities are tightly coupled. Changes in one synthesis area significantly affect the others. Hardware synthesis activities include selecting the programmable processor, which directly impacts the

software synthesis activity of selecting a code generator, and determining the appropriate number of processors and their connectivity, which, in turn, influences the code partitioning decision and hardware/software interface synthesis. Choices involved in custom hardware synthesis can range from generating custom data paths to generating masks for FPGAs. As a part of custom data path design, the register word lengths must be selected (Kalavade and Lee, 1993).

Depending on the chosen hardware configuration, software synthesis can involve partitioning and scheduling the code across multiple processors and synthesizing the code for interprocessor communication—decisions which depend heavily upon the selected architecture. Partitioning among different processors may be performed with the intent of optimizing cost functions such as communication cost, memory bandwidth, and local and global memory sizes. In addition, if the hardware configuration includes use of fixed-point processors, some algorithmic modifications might be required to minimize finite precision effects, such as limit cycles and quantization errors (Kalavade and Lee, 1993).

Interface synthesis involves adding latches, FIFO (first in, first out) registers, or address decoders in hardware and adding code to handle input/output operations and semaphore synchronization in software. Iterating to explore different design options is the common method for solving this cyclic problem (Kalavade and Lee, 1993).

After the hardware, software, and interface synthesis tasks have been accomplished, the hardware/software system design can be simulated within a heterogeneous simulation environment. Since the simulated hardware must run the generated software, the simulation environment should allow for the interaction of a number of different simulators in the event that various specification languages are used.

Simulation results can then be used to verify that the design works as intended and meets the given system specifications. If the specifications are not satisfied, another iteration will be needed. Whether it is necessary to perform another iteration of the entire codesign process or just portions of the process will depend on the nature of the shortcoming. The simulation results and the hardware and software configurations chosen for the specific system design can also be used to evaluate the system in terms of performance and estimates of other factors including power requirements, die area, component and bus utilization, and manufacturing costs. After using these estimates to evaluate the design, the designer may choose to repartition the system and experiment with different designs (Kalavade and Lee, 1993).

Currently, there are several programs that are developing design environments which support hardware/software codesign or are attempting to incorporate those ideas into

a larger system engineering methodology while developing the enabling tools. The next two sections provide a sample of these efforts.

# 2.3.2 The Ptolemy Project

Developed at the University of California at Berkeley, Ptolemy is an environment for prototyping and simulating heterogeneous systems.<sup>9</sup> Heterogeneous systems are systems involving subsystems having different models of computation and, hence, fundamentally different approaches to design and simulation. According to Dr. Mark Richards of ARPA, Ptolemy's framework allows a designer to mix and match multiple models of computation more effectively than most design systems. Ptolemy facilitates the interaction of diverse models of computation through the use of object-oriented principles of polymorphism and information hiding.

Since the start of the Ptolemy project in 1990, there have been numerous advances in design, simulation, and code generation. Many of these advances have been incorporated in Ptolemy in the realms of dataflow modeling of algorithms, synthesis of embedded software from such dataflow models, animation and visualization, multidimensional signal processing, hardware/software partitioning, VHDL (VHSIC Hardware Description Language) code generation, and managing complexity through the use of higher-order functions.<sup>10</sup>

Ptolemy employs object-oriented software principles in attempting to achieve the following goals (Buck et al., 1994):

Agility. The Ptolemy environment should support distinct computational models to enable each subsystem to be simulated and prototyped in a manner that is appropriate and natural to that subsystem.

<sup>&</sup>lt;sup>9</sup> The Ptolemy software is available for the Sun 4 (sparc), DecStation (MIPS), and HP-PA architectures. System installation requires 90MB of disk space and at least 8MB of physical memory. A scaled-down demonstration version, called Ptiny Ptolemy, is also available for the same architectures but only requires 12MB of disk space. A copy of Ptolemy can be obtained on tape by calling (510) 643-6687 or via anonymous ftp from ptolemy.eecs.berkeley.edu. Other on-line information resources can be found in the newsgroup comp.soft-sys.ptolemy and on the World Wide Web at http://ptolemy.eecs.berkeley.edu.

<sup>&</sup>lt;sup>10</sup> The project joined ARPA's RASSP program, the subject of the next section, in 1993 as a technology base developer.

- *Heterogeneity*. Ptolemy should enable distinct computational models to coexist seamlessly in order to investigate interactions among subsystems.

- *Extensibility.* Ptolemy should support seamless integration of new computational models and allow them to interoperate with existing models with no modifications to the Ptolemy environment or existing models.

- *Friendliness*. Ptolemy should employ a modern graphical interface with a hierarchical block diagram style of representation.

Ptolemy has been used for a wide range of applications including signal processing, telecommunications, parallel processing, wireless communications, network design, radio astronomy, real-time systems, and hardware/software codesign.

In the hardware/software codesign application area, Ptolemy is a very powerful tool since all parts of a hardware/software system can be modeled using the various domains included in the environment. Modeling both hardware and software within a single framework allows a designer to explore tradeoffs between hardware and software implementations of different functions (Buck et al., 1994). Another advantage of being able to develop hardware and software simultaneously in a design and simulation environment is that software development does not have to wait for a hardware prototype to be ready in order to start. In fact, if the manufactured hardware configuration is the same as the simulated hardware/software system, the actual production software code will have already been developed and verified.<sup>11</sup>

### 2.3.3 Rapid Prototyping of Application Specific Signal Processors<sup>12</sup>

Initiated in 1993, the Rapid Prototyping of Application Specific Signal Processors (RASSP) program is a four-year ARPA/Tri-Service initiative aimed at creating a new process for the development of military signal processors. The program's objective is to

<sup>&</sup>lt;sup>11</sup> A good example of how Ptolemy can be used in hardware/software codesign to explore the design space can be found in Kalavade (1991).